# Two-dimensional Analytical Drain Current Model for Multilayered-Gate Material Engineered Trapezoidal Recessed Channel (MLGME-TRC) MOSFET: a Novel Design

Priyanka Malik A, Rishu Chaujar B, Mridula Gupta C, R.S. Gupta D

Abstract—In this paper, for the first time, a two-dimensional (2D) analytical drain current model for sub-100 nm multi-layered gate material engineered trapezoidal recessed channel (MLGME-TRC) MOSFET: a novel design is presented and investigated using ATLAS and DEVEDIT device simulators, to mitigate the large gate leakages and increased standby power consumption that arise due to continued scaling of SiO2-based gate dielectrics. The two-dimensional (2D) analytical model based on solution of Poisson's equation in cylindrical coordinates, utilizing the cylindrical approximation, has been developed which evaluate the surface potential, electric field, drain current, switching metric: ION/IOFF ratio and transconductance for the proposed design. A good agreement between the model predictions and device simulation results is obtained, verifying the accuracy of the proposed analytical model

*Keywords*—ATLAS, DEVEDIT, NJD, MLGME- TRC MOSFET.

### I. INTRODUCTION

STEADY downscaling of device dimensions, innovative device designs and rapid advances in technology are some of the factors that have largely governed the evaluation of CMOS technology at a remarkable rate over the last few decades. As a result denser and faster integrated circuits have been achieved that offer superior performance and much reduced physical size compared to their predecessors. However, the continued miniaturization of MOSFETs in sub-100nm regime, further scaling down of SiO<sub>2</sub> gate dielectric leads to high direct tunneling gate leakage current, which in turn causes increase in device power consumption. To reduce the gate leakage current in small geometry MOSFETs, high-k gate dielectrics emerged as an alternative to conventional SiO2. A high-k gate dielectric layer [1, 2] allows physically thicker films while permitting smaller electrical thickness. It

Authors A, C and D are with the Semiconductor Devices Research Laboratory, Department of Electronic Science, University of Delhi, South Campus, New Delhi (India)-110021 (corresponding author phone: 91-11-24115580; Fax No: 91-11-24110606, E-Mail: rsgu@bol.net.in , prin.malik@gmail.com).

Author B, is Department of Electronics, Deen Dayal Upadhyaya College, Karampura, University of Delhi, New Delhi-110015 (e-mail: rishuchaujar@rediffmail.com).

increases the gate control over the channel, but gives rise to unacceptable levels of interface traps [3], bulk fixed charges, low interface carrier mobility and phase instability issues [4]. Thus, it gives way to a gate stacked engineered structure [5, 6] that uses the stack of a thin SiO2 and a thick high-k layer. Thus, an ultra thin SiO2 interlayer between the high-K layer and silicon substrate was introduced (resulting in a multi-layer gate structure) to improve the interface quality and stability. Further, to achieve higher speeds and higher packing densities, gate length miniaturization is the key parameter, but it leads to many SCEs and hot carrier effects.

Multilayered Gate Material Engineered Trapezoidal Recessed Channel (MLGME-TRC) MOSFET design, considered in this study integrates the desired features of multi-layered gate architecture [7,8] such as improvement in gate controllability and reduction in gate leakage and tunneling effects; and those allied with GME-TRC [9] and RC MOSFET [10,11] such as excellent hot carrier immunity, SCE and punchthrough suppression, thereby enhancing the gate controllability over the channel and the electrical and switching characteristics in terms of DIBL, subthreshold swing and hot carrier effects. Thus, multi-layered dielectric gate architecture in conjunction with recessed channel structure is of paramount importance in nanoscale devices which in turn enhances the gate controllability, current driving capabilities, ION/IOFF ratio and transconductance across the channel.

Further, to gain insight into the effectiveness of MLGME-TRC MOSFET design, a simple 2D analytical model has been developed by solving the 2D Poisson equation in cylindrical coordinates, utilizing the cylindrical approximation, and compared with conventional gate material engineered trapezoidal recessed channel (GME-TRC) and trapezoidal recessed channel (TRC) MOSFETs. The device simulators: ATLAS and DEVEDIT [12] have been used to verify the accuracy of the proposed model, and a good agreement between their results is obtained. The proposed design proves its efficacy for improved high performance analog and switching applications.

#### II. MODEL FORMULATION

### 1. Two dimensional potential and Electric field profile

#### 1.1 Potential analysis:

In the present analysis, the channel region is divided into two parts, since the gate is made up of two different materials laterally merged together. Assuming the concave corner to be

part of a cylinder, having radius

$$r_o = \frac{L_p}{2(1 + \tan \theta_{o1}/2)}$$

[13],

Poisson equation in cylindrical coordinates for potential, i.e.  $\psi(r,\theta)$ , is given by

$$\frac{\partial^{2}\psi(r,\theta)}{\partial r^{2}} + \frac{1}{r}\frac{\partial\psi(r,\theta)}{\partial r} + \frac{1}{r^{2}}\frac{\partial^{2}\psi(r,\theta)}{\partial\theta^{2}} = \frac{qN_{A}}{\varepsilon_{Si}}$$

In the present analysis, the channel region has been divided in to two parts; hence the potential under the gate region M1 and M2 can be represented as

$$\psi_{1}(r,\theta) = A_{01}(\theta) + A_{11}(\theta)r + A_{21}(\theta)r^{2}$$

for  $0 \langle \theta \langle \theta_{01} \rangle$ ;  $r_{o} + EOT \langle r \langle r_{o} + EOT + y_{d} \rangle$

$$\psi_{2}(r,\theta) = A_{02}(\theta) + A_{12}(\theta)r + A_{22}(\theta)r^{2}$$

$$for \quad \theta_{01} \langle \theta \langle \theta_{01} + \theta_{02} ; r_{o} + EOT \langle r \langle r_{o} + EOT + y_{d} \rangle$$

Where, depletion layer thickness is given by  $y_d = \sqrt{\frac{2\varepsilon_{Si}}{qN_A}}1.5\phi_F$

And the effective gate oxide thickness, EOT, is given by

$$EOT = t_{ox1} + \frac{\mathcal{E}_{ox1}}{\mathcal{E}_{ox2}} t_{ox2} ,$$

Based on boundary conditions, as shown in Fig.1. the Poisson's equation is solved separately under the two gate regions (M1 and M2) and the potential can be calculated as:

$$\psi_{j}(r,\theta) = V_{SUB} + \frac{1}{\gamma} \left( \frac{1}{r_{o} \ln(1 + EOT/r_{o})} \right) \cdot \left( V_{gj} - \psi_{Sj}(\theta) \right).$$

$$\left[ -\frac{(r_{o} + EOT + y_{d})^{2}}{2y_{d}} + \frac{(r_{o} + EOT + x_{d})^{2}}{y_{d}} r - \frac{1}{2y_{d}} r^{2} \right]$$

where, i = 1,2 for regions under M1 and M2 respectively.

# 1.2 Electric field analysis:

The electron velocity through the channel is related to the electric field pattern along the channel. Thus, the electric field is given as

$$E_{Sj}(\theta) = -\frac{d}{r.d\theta} \psi_j(r,\theta) \Big|_{r=r_o+EOT} = -\frac{d}{r.d\theta} \psi_{Sj}(\theta)$$

where,  $r = r_o + EOT$

Electric field component, under M1 is given as

$$E_{s1}(\theta) = \frac{1}{r \cdot \lambda \sinh(\theta_{\perp}/\lambda)} \left\{ \delta_{11} \cosh\left((\theta_{o1} - \theta)/\lambda\right) - \delta_{12} \cosh(\theta/\lambda) \right\}$$

Electric field component, under M2 is given as

$$E_{S2}(\theta) = \frac{1}{r \cdot \lambda \sinh(\theta_{o2}/\lambda)}.$$

$$\left\{ \delta_{21} \cosh \left( (\theta_{o1} + \theta_{o2} - \theta) / \lambda \right) - \delta_{22} \cosh \left( (\theta - \theta_{o1}) / \lambda \right) \right\}$$

## 2. Drain current and transconductance profile

In this section,  $I_{ds}$ - $V_{gs}$  model for the proposed design incorporation with channel length modulation (CLM) effect for linear to saturation region has been summarized [14].

Case.I. linear region

$$I_{ds} = \frac{\mu . C_{oxc}.W}{L_{eff}.\left(1 + \frac{\delta_o.V_{ds}}{L_{eff}.\mathcal{E}_c}\right)}.(V_{gs} - V_{th} - 0.5.\alpha.V_{ds})$$

Case.II Saturation region

$$I_{ds} = \frac{\mu . C_{oxc}.W}{\left(L_{eff} - l_{d}\right).\left(1 + \frac{\delta_{o}.\mu_{s}.V_{ds}}{\left(L_{eff} - l_{d}\right).\nu_{sat}}\right)}.(V_{gs} - V_{th} - 0.5.\alpha.V_{dsx}).V_{dsx}$$

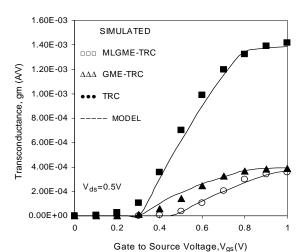

Transconductance:

Transconductance is an important device parameter for analog circuit simulation and can be calculated as:

$$g_{m} = \frac{\partial I_{ds}}{\partial V_{gs}} \Big|_{V_{ds} = constant}$$

# III. RESULT AND DISCUSSION

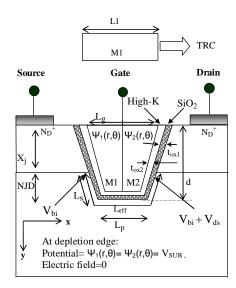

The schematic structure of MLGME-TRC MOSFET is shown in Fig.1. with metal gates, M1 and M2 of lengths L1 and L2 respectively. In MLGME-TRC MOSFET, the gate consists of multi-layered-gate dielectrics having a thickness  $t_{\rm ox1}$  and  $t_{\rm ox2}$  of the lower and the upper gate dielectrics with the corresponding permittivites,  $\epsilon_{\rm ox1}$  and  $\epsilon_{\rm ox2}$ , respectively; and for GME-TRC and TRC MOSFETs:  $t_{\rm ox1} = t_{\rm ox2}$ .

Fig.1.Schematic structure of MLGME-TRC MOSFET, where channel length  $L_g = L_1 + L_2$  =74nm, with work function  $\Phi_{M1} \!=\! 4.77V$  and  $\Phi_{M2} = 4.10V$  for MLGME-TRC and GME-TRC MOSFET and for TRC MOSFET, channel length  $L_g \!=\! L_1 \!=\! 74$ nm and work function  $\Phi_{M1} \!=\! 4.77V$  having Negative junction depth (NJD)=10nm, Groove Depth d=20nm,  $N_A = 1 \times 10^{17}$  cm $^3$ ,  $N_D \!=\! 1 \times 10^{20}$  cm $^3$ ,  $t_{ox1} \!=\! t_{ox2} \!=\! 2nm$ ,  $L_{eff} \!=\! (2 \times L_s) + L_p$ , where  $L_p \!=\! 28$ nm,  $L_s \!=\! 14$ nm unless stated otherwise.

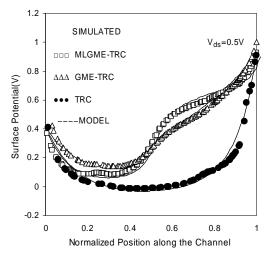

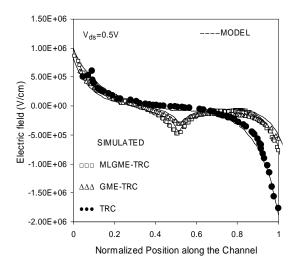

Fig.2. and Fig.3. shows the modeled and simulated results for potential and electric field profile for MLGME-TRC, GME-TRC and TRC MOSFETs. A close proximity between the modeled and simulated results validates the proposed model. Simulation results reveal that TRC-MOSFET with GME architecture improves the device performance with the use of two metal gates i.e. M1(control gate) and M2 (screening gate) where  $\Phi M1 > \Phi M2$ , in terms of improved gate control and driving current capabilities. This is due to the step in surface potential at the interface of two metals, which results in screening of channel region under metal gate M1 from drain potential variations and hence ensures reduction in DIBL and punch through effects. Further, the significant enhancement in step of potential profile for MLGME-TRC MOSFET, as shown in Fig.2., in comparison with GME-TRC MOSFET is due to improvement in screening effect as a consequence of the incorporation of multi-layered high-K dielectric system that facilitates physically thicker gates, thereby permitting the scaling of gate oxide thickness and thus, increasing gate control over the channel. Fig.3. clearly depicts that for GME-TRC MOSFET, the step in potential forces the electric field to be redistributed on the drain side. This electric field discontinuity at the interface of the two gate metals causes the overall channel field to be more uniform across the channel resulting in the enhancement of carrier transport efficiency across the channel. For, MLGME-TRC MOSFET, the peak in electric field further increases at the interface thereby, improving the current driving capabilities across the channel, due to the improved gate control and hot carrier immunity for ML-GME-TRC MOSFET.

Fig. 2. Potential profile for ML-GME-TRC, GME-TRC and TRC MOSFETs having  $\epsilon_{ox1}$ =3.9 and  $\epsilon_{ox2}$ =20. The solid line represents the modeled results.

Fig. 3. Electric field profile for ML-GME-TRC, GME-TRC and TRC MOSFETs having  $\epsilon_{ox1}$ =3.9 and  $\epsilon_{ox2}$ =20. The solid line represents the modeled results.

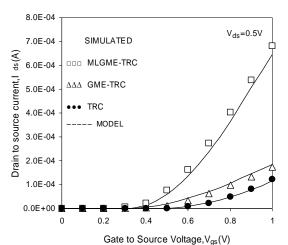

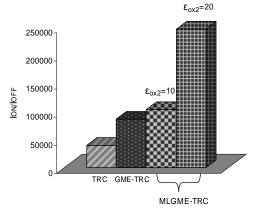

Fig.4, 5 and 6 shows the drain current, transconductance ION/IOFF ratio profile, respectively, for MLGME-TRC, GME-TRC and TRC MOSFETs. For GME-TRC MOSFET, the step in potential profile results in a more uniform electric field across channel, leading to improved driving current, transconductance, and ION/IOFF ratio as shown in Fig.4, 5 and 6, respectively. The amalgamation of multilayered gate stack and GME-TRC MOSFET, further enhances the peak electric field at the interface, there by improving the drain current and hence the transconductance and switching speed in terms of ION/IOFF ratio as shown in Fig.4, 5 and 6, respectively, due to the improved gate control and; reduces short channel and hot carrier effects for MLGME-TRC MOSFET.

Fig. 4. Drain to Source current Vs Gate to source Voltage( $V_{gs}$ ) for ML-GME-TRC, GME-TRC and TRC MOSFETs having  $\epsilon_{ox1}$ =3.9 and  $\epsilon_{ox2}$ =20The solid line represents the modeled results.

Fig. 5. Transconductance Vs Gate to source Voltage( $V_{gs}$ ) for ML-GME-TRC, GME-TRC and TRC MOSFETs having  $\epsilon_{ox1}$ =3.9 and  $\epsilon_{ox2}$ =20. The solid line represents the modeled results.

Fig. 6. Simulated  $I_{ON}/I_{OFF}$  variation for ML-GME-TRC, GME-TRC and TRC MOSFETs having  $\epsilon_{ox1}$ =3.9. The solid line represents the modeled results.

## IV. CONCLUSION

In this work, a novel structure, MLGME-TRC MOSFET has been proposed, analyzed and investigated using device simulators: ATLAS and DEVEDIT. Continued scaling of SiO2-based gate dielectrics necessitates the introduction of high-K materials for sub-100 nm technology node. The analytical and simulation results reveal that, MLGME-TRC MOSFET proves to be superior to GME-TRC and TRC MOSFETs in terms of improved gate controllability, enhanced electric field across the channel and thus, increased driving current, transconductance and switching characteristic in terms of ION/IOFF ratio. The proposed MLGME-TRC design, hence, presents its applicability for high speed logic and low standby power (LSP) applications.

#### ACKNOWLEDGEMENT

Authors are grateful to Department of Science and Technology (DST) for providing the necessary financial assistance to carry out this research work.

#### REFERENCES

- S.A. Campbell, D.C. Gilmer, X. Wang, M. Hsieh, H-S. Kim, W.L. Gladfelter and J. Yan, "MOSFET transistors fabricated with high permittivity TiO2 dielectrics" *IEEE Trans. Electron Devices* vol. 44, pp.104–109, (1997).

- [2] W. Tsai et a,1 "Performance comparison of sub 1 nm sputtered TiN HfO2 nMOS and pMOSFETs" IEDM Tech., Dig. 311–314, (2003).

- 3] H. Kimura, J. Mizuki, S. Kamiyama and H. Suzuki, "Extended x-ray absorption fine structure analysis of the difference in local structure of tantalum oxide capacitor films produced by various annealing methods" Appl. Phys. Lett. Vol. 66, pp.2209–2211, (1995).

- [4] J-L Autran, D. Munteanu, M. Houssa, K. C. Coulie and A. Said, "Performance degradation induced by fringing field-induced barrier lowering and parasitic charge in double-gate metal-oxide semiconductor field-effect transistors with high-ê dielectrics" *Japan. J. Appl. Phys.* Vol. 44, 8362–6, (2005).

- [5] S.J. Lee, C.H. Choi, A. Kamath, R. Clark and D.L. Kwong, "Characterization and reliability of dual high-k gate dielectric stack (poly-Si-HfO2-SiO2) prepared by in situ RTCVD process for system-on-chip applications" IEEE Electron Device Lett. Vol. 24, 105–107, (2003).

- [6] T. Kauerauf, B. Govoreanu, R. Degraeve, G. Groeseneken and H. Maes, "Scaling CMOS: finding the gate stack with the lowest leakage current" Solid-State Electron. Vol. 49, 695–701, (2005).

- [7] B.Cheng, M. Cao, R. Rao, A. Inani, P.V. Voorde, W.M. Greene, J.M.C. Stork, Z. Yu, P.M. Zeitoff and J.C.S. Woo, "The impact of high-k gate dielectrics and metal gate electrodes on sub-100 nm MOSFETs" IEEE Trans. Electron. Devices Vol. 46, pp. 1537, (1999).

- [8] J. Zhang, J.S. Yuan and Y. Ma "Modeling short channel effect on highk and stacked gate MOSFETs" Solid-State Electron. Vol.44, pp. 2089, (2000).

- [9] P.Malik, S.P.Kumar, R.Chaujar, M.Gupta, R.S.Gupta, "GATE MATERIAL ENGINEERED-TRAPIZIODAL RECESSED CHANNEL MOSFET FOR HIGH-PERFORMANCE ANALOG AND RF APPLICATIONS", Microwave and optical technology letters, Vol.52, march 2010.

- [10] P.H. Bricout and E. Dubois "Short-channel effect immunity and current capability of sub-0.1-micron MOSFETs using a recessed channel" *IEEE Trans. Electron. Devices* Vol.43, pp.1251 (1996).

- [11] H. Ren and Y. Hao "The influence of geometric structure on the hot-carrier-effect immunity for deep-sub-micron grooved gate PMOSFET Solid-State Electron". Vol.46, pp. 665 (2002).

- [12] ATLAS: 3-D and DEVEDIT: 3D Device Simulator SILVACO International (2002).

# International Journal of Electrical, Electronic and Communication Sciences

ISSN: 2517-9438 Vol:4, No:4, 2010

- [13] X.J. Zhang, H.X. Ren, Q. Feng and Y. Hao, Chin. J. Semiconductors, Vol.25, pp. 441, (2004) (in chinese)

- [14] N.D. Arora, R.Rios, C-L Huang and K. Raol, "PCIM: A Physically Short-Channel IGFET Model for Circuit Simulation" *IEEE Trans. Electron Devices*, Vol.41, June 1994.