# Investigation of the Effects of Sampling Frequency on the THD of 3-Phase Inverters Using Space Vector Modulation

Khattab Ibrahim Al Qaisi, Nicholas Bowring

Abstract—This paper presents the simulation results of the effects of sampling frequency on the total harmonic distortion (THD) of three-phase inverters using the space vector pulse width modulation (SVPWM) and space vector control (SVC) algorithms. The relationship between the variables was studied using curve fitting techniques, and it has been shown that, for 50 Hz inverters, there is an exponential relation between the sampling frequency and THD up to around 8500 Hz, beyond which the performance of the model becomes irregular, and there is an negative exponential relation between the sampling frequency and the marginal improvement to the THD. It has also been found that the performance of SVPWM is better than that of SVC with the same sampling frequency in most frequency range, including the range where the performance of the former is irregular.

**Keywords**—SVPWM, THD, DC-AC Inverter, Sampling Frequency.

#### I. INTRODUCTION

${f R}^{\hbox{\scriptsize ECENT}}$  interests in renewable energy resources has placed onerous demands on power electronic converters which are fundamental to the harvesting and harnessing of the renewable energy such as solar and wind energy. One such type of converters is the voltage-sources inverter (VSI). VSIs are used in many applications that require conversion of a DC voltage into sinusoidal AC voltage. In a renewable energy system such as photovoltaic (PV), the harvested energy is typically used to charge a bank of batteries which is subsequently converted to an AC voltage and either used directly or integrated with the low-voltage utility grid [1]. It is ideal that an inverter generates a sinusoidal waveform of the same quality as that of the grid, but the AC voltage generated by a DC through the modulation of switches usually contains distortion in the form of higher harmonics, so it is important to reduce the total harmonic distortion (THD) as much as possible before the inverter can be interfaced with the grid. Various inverter modulation and control schemes have been developed for a variety of inverter topologies covering both single and multilevel inverters. Different topologies may require components with different electric characteristics such as tolerable range of switching frequencies, and these could affect the cost of implementation.

Khattab Ibrahim Al Qaisi and Nicholas Bowring are with the School of Engineering, The Manchester Metropolitan University, John Dalton Building, Chester Street, Manchester M1 5GD, UK (phone: +44 (0)161 247 2000; fax: +44 (0)161 247 6390; e-mail: khattab.al-qaisi@stu.mmu.ac.uk, n.bowring@stu.mmu.ac.uk)

Space vector provides a useful tool for the design of three phase inverter with good performance. Many recent researches for instance, [2]-[6], have indicated to the good performance characteristics of space vector pulse width modulation (SVPWM), but there is no mention of how the sampling frequency affects the performance of such a design, and such information would be valuable as sampling frequency is a major parameter that affects the cost and circuit complexity. The current work is to use models to investigate the performance of space vector pulse width modulation (SVPWM) and the effects of the sampling frequency, which is set in relation to the output frequency, in reducing THD.

#### II. SPACE VECTOR PWM

In many cases, there is the need to generate three phase AC output from a DC source. The topology used can be seen as an extension of the H-Bridge topology. The three output points of the inverter are connected to the three legs of a three-phase load. Inside the inverter, each of these output points is switched to either of its two input voltage  $+V_{dc}/2$  and  $-V_{dc}/2$  in any instance. There are eight combinations of these three switching positions, and each combination or state results in a specific voltage difference amongst the output points [7]-[9]. Changing from one state to another involves changing one or more switches. By arranging the sequence of states and the durations of each state, three sinusoidal outputs with  $2\pi/3$ phase difference between successive ones could be generated. Furthermore, with appropriate arrangement, the transition from one state to the next would only require the change of one switch's position. This could not only avoid voltage surge due to unsynchronized switching between two switches, but also reduce the overall switching frequencies, and the avoidance of the frequent switching, which is common to many time modulation algorithms, reduces the chance of generation of electromagnetic inference or noise. Additionally, the combination of the binary switching positions lends well to digital control of modulation [10].

Hence, by properly arranging this sequence of switch combinations resulting in a sequence of varying voltage output, a step wave mimicking a sinusoidal wave could be generated whilst each time the position of only one switch is changed between the switching states of successive time intervals.

Space vector provides a useful tool to simplify the task of help determine a suitable state sequence and the duration of each state to achieve the desired outputs. Instead of time-

lapsed sinusoidal waves on a real number plane, the state of the system is represented by a state vector on a complex number plane called a vector space. Thus the behavior of a sinusoidal wave of frequency f is represented by a vector  $V_{\rm ref}$  of constant magnitude rotating around the origin at an angular frequency  $\omega$  where  $\omega = 2\pi f$  and the magnitude of the vector  $|V_{\rm ref}|$  is equal to the amplitude of the sine wave [11], [12]. According to Euler's formula,

$$e^{jt} = \cos \omega t + j \sin \omega t \tag{1}$$

$$e^{j(\omega t + \varphi)} = \cos(\omega t + \varphi) + j\sin(\omega t + \varphi)$$

(2)

Thus, the projection of the reference vector on the real axis is the formula for the sinusoidal wave, and difference phase are represented by difference angles.

As stated before, each state represents a combination of switch positions. If the switching position for the high voltage is denoted by 1 and the one to the low voltage 0, the state of (1,0,0) denotes the state where only the first switch is switched to the high voltage whilst the others are switched to the low voltage. If the phase of this state is set as 0, the vector representing this state is a vector of magnitude  $V_{dc}/2$  along the positive real axis. Because the phase difference between the outputs is  $2\pi/3$ , the state (0,1,0) is denoted by a vector of the same magnitude but with an angle  $2\pi/3$ . Likewise, the state (0,0,1) is denoted by a vector of the same magnitude but with an angle  $4\pi/3$ . States (0,0,0) and (1,1,1) result in no voltage difference amongst the output pints, so both are represented by the origin of the coordination system.

The state (0,1,1) represents a negation of the state (1,0,0)and the representing vector rests in the negative direction of the real axis. Likewise, the states (1,0,1) and (1,1,0) can be represented in the same vector space. The result reveals that all eight possible states rest on the origin and the vertexes of the normal hexagon centered at the origin. The hexagon can be divided into six equilateral triangles, and the transition between the neighboring states resting on the vertexes of these triangles involves the change of one switching position. The biggest circle that can fit into this hexagon represents the path of the reference vector for the biggest sine wave that could be generated by the inverter. As the sine wave propagates, the reference vector in this vector space sweeps through the six triangular regions, and it could be represented by the vector combination of the states whose vectors rest on two of the vertices of the triangle. From this visualization, the sequence of switching states and the duration of each state needed for the desired outcome can be determined.

## III. MODEL

The relevant state vectors forming the sequence are chosen based on the region number r, and the region number is determined by the angle of the reference vector. To avoid ambiguity and unexpected results when the reference vector aligns with any of the state vectors, a small angular displacement is added to the angle in the calculation.

One possible switching sequence where there is only one

switch is changed in every state transition can be determined based on the diagram above, starting from  $V_7$  in each region and first follow the arrows in that region then reverse back to  $V_7$ . This sequence is listed in the Table I.

Based on this,  $T_a$ ,  $T_b$ ,  $T_c$ , the duration in which the three switches a, b, c need to be switched on during the relevant sampling time  $T_s$ , could be determined based on their relation with  $T_0$ ,  $T_r$  and  $T_{r+1}$ , the duration in which the system stays in the null state ( $\mathbf{V}_7$  or  $\mathbf{V}_0$ ) and the two states whose state vectors' end points rest on the other two vertices of the triangular region (e.g.,  $\mathbf{V}_1$  and  $\mathbf{V}_2$  for the  $1^{st}$  region). For instance, in the  $1^{st}$  region, switch a is always on, so the time it is switched on is  $T_a = T_0 + T_r + T_{r+1}$  and  $T_c = T_0 + T_{r+1}$  in the  $4^{th}$  region. Thus,  $T_a$ ,  $T_b$ ,  $T_c$  for all six regions based on  $T_0$ ,  $T_r$ ,  $T_{r+1}$  are listed in Table II.

TABLE I ONE POSSIBLE STATE TRANSITION AND SWITCHING SEQUENCE

| Duration | T <sub>0</sub> | T <sub>r</sub> / 2 | $T_{r+1}$      | T <sub>r</sub> / 2 | T <sub>0</sub> |

|----------|----------------|--------------------|----------------|--------------------|----------------|

| Region   | $V_7$          | $\mathbf{V}_2$     | $\mathbf{V}_1$ | $\mathbf{V}_2$     | $V_7$          |

| 1        | (1,1,1)        | (1,1,0)            | (1,0,0)        | (1,1,0)            | (1,1,1)        |

| Region   | $V_7$          | $\mathbf{V}_2$     | $V_3$          | $\mathbf{V}_2$     | $V_7$          |

| 2        | (1,1,1)        | (1,1,0)            | (0,1,0)        | (1,1,0)            | (1,1,1)        |

| Region   | $V_7$          | $V_4$              | $V_3$          | $V_4$              | $V_7$          |

| 3        | (1,1,1)        | (0,1,1)            | (0,1,0)        | (0,1,1)            | (1,1,1)        |

| Region   | $V_7$          | $V_4$              | $V_5$          | $V_4$              | $V_7$          |

| 4        | (1,1,1)        | (0,1,1)            | (0,0,1)        | (0,1,1)            | (1,1,1)        |

| Region   | $V_7$          | $V_6$              | $V_5$          | $V_6$              | $V_7$          |

| 5        | (1,1,1)        | (1,0,1)            | (0,0,1)        | (1,0,1)            | (1,1,1)        |

| Region   | $V_7$          | $V_6$              | $\mathbf{V}_1$ | $V_6$              | $V_7$          |

| 6        | (1,1,1)        | (1,0,1)            | (1,0,0)        | (1,0,1)            | (1,1,1)        |

TABLE II THE RELATIONS BETWEEN  $T_{\rm a},\,T_{\rm B},\,T_{\rm C}$  and  $T_{\rm 0},\,T_{\rm R+1},\,T_{\rm R}$  for Each of the Six Regions

| Region | Ta    |         |           | T <sub>b</sub> |         |           | T <sub>c</sub> |         |           |  |

|--------|-------|---------|-----------|----------------|---------|-----------|----------------|---------|-----------|--|

|        | $T_0$ | $T_{r}$ | $T_{r+1}$ | $T_0$          | $T_{r}$ | $T_{r+1}$ | $T_0$          | $T_{r}$ | $T_{r+1}$ |  |

| 1      | 1     | 1       | 1         | 1              | 0       | 0         | 1              | 1       | 0         |  |

| 2      | 1     | 1       | 1         | 1              | 0       | 1         | 1              | 0       | 0         |  |

| 3      | 1     | 1       | 0         | 1              | 1       | 1         | 1              | 0       | 0         |  |

| 4      | 1     | 0       | 0         | 1              | 1       | 1         | 1              | 0       | 1         |  |

| 5      | 1     | 0       | 0         | 1              | 1       | 0         | 1              | 1       | 1         |  |

| 6      | 1     | 0       | 1         | 1              | 0       | 0         | 1              | 1       | 1         |  |

|        |       |         |           |                |         |           |                |         |           |  |

$T_0$ ,  $T_r$ ,  $T_{r+1}$  are determined [13]-[15] by the following formulae:

$$T_r = A(\sin\frac{\pi}{3}r \cdot \cos\omega t - \cos\frac{\pi}{3}r \cdot \sin\omega t)$$

(3)

$$T_{r+1} = A(\cos\frac{\pi}{3}(r-1)\cdot\sin\omega t - \sin\frac{\pi}{3}(r-1)\cdot\cos\omega t) \quad (4)$$

where

$$A = \sqrt{3}T_s \frac{v_{ref}}{v_{dc}} \tag{5}$$

$$T_0 = (T_s - T_r - T_{r+1}) / 2$$

$$T_0 = \frac{1}{2}(T_s - T_r - T_{r+1}) \tag{6}$$

#### IV. IMPLEMENTATION

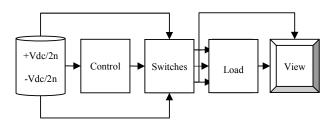

Based on the mathematic model, a simulation model was built through several iterations. First the following schematic diagram was devised for the model:

Fig. 1 Simulink model of three phase SVPWM using simple components

Based on this schematic diagram, the model was first built using simple components. Global parameters were initialized within the initialization function.

The model was then modified by using a MATLAB function to encapsulate the part that determines the values of Ta, Tb and Tc. For these first two models, the effects of some global parameters on the performance of the model could be qualitatively checked by changing the values in the initialization function and visually check the output curves generated by the model.

This model was then further modified to reduce the input to the system to Vdc, Vref, f and clock, and let the MATLAB function block calculate the other parameters accordingly. The sampling frequency  $f_s$  was also set here as an integer multiple of the output frequency f. THD values were calculated for the outputs and displayed. Thus, with this model, different values of  $f_s$  and the corresponding THD values could then be recorded for further analysis.

### V. FINDINGS

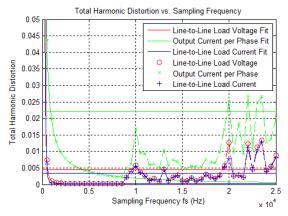

Different values of  $f_s$  as integer multiples of f had been used for testing and the resulting THD readings were recorded. The relationship between the sampling frequency and the THD were shown in functional graphs.

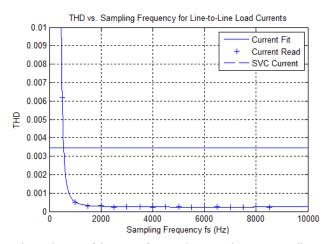

Fig. 2 Total harmonic distortion vs. sampling frequency

For the output frequency of 50 Hz, the sampling frequency has been set from 500 Hz to 15000 Hz in 500 Hz increments. The THD readings collected follow an inverse exponential decrease with sampling frequency up to around 8500 Hz where the graphs of THDs of both line voltage and current between phases vs. sampling frequency reach the minimum of 0.000240, whilst the graph of THD of current per phase vs. sampling frequency reaches the minimum of 0.002297.

From then on, the readings become irregular but the order of magnitude increases by one. This could be due to increased electromagnetic interference caused by high switching frequency as well as not being able to accurately divide further the already small sampling time into fractions for different states in each sampling time.

Taking as a reference for comparison as well as testing the contribution of rounding errors in high frequency situations, the control function of the model was modified to adopt the space vector control algorithm instead. This was done by removing the division of  $T_0$  into  $T_s$ ,  $T_r$  and  $T_{r+1}$ , and instead setting  $T_r$  as  $T_0$ , and  $T_s$  and  $T_{r+1}$  as 0, thus avoiding the introduction of rounding errors. This in effect turned off pulse width modulation based on the region in which the phase angle falls. The result was that the THD for each of the line voltage, current per phase and current between phases remains constant irrespective of the sampling frequency. Comparing this constant with the THD of the SVPWM design in high frequency revealed that, at least up to 19000 Hz, the THD of the latter is still much less than that of the former. In other words, even though there was electromagnetic interference due to high switching frequency, the rounding errors in further dividing each time slot did not seem to be very important. Additionally, though the performance of SVC might be acceptable to many applications and it has the advantages of simplicity and low switching frequency, its performance is not as good as that of SVPWM.

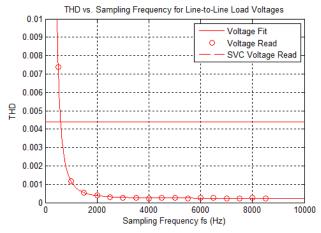

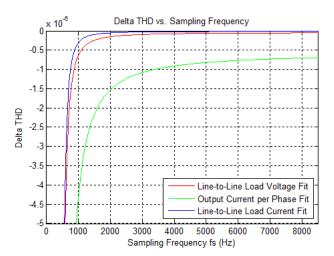

Fig. 3 Diagram of the THD of line voltage vs. sampling frequency

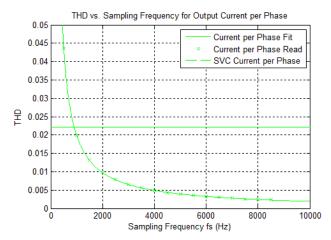

Fig. 4 Diagram of the THD of current per phase vs. sampling frequency

Fig. 5 Diagram of the THD of current between phases vs. sampling frequency

Fig. 6 Diagram of improvement of THD vs. sampling frequency

Moreover, to further investigate the functional relation between THD and sampling frequency up to 8500 Hz, curve fitting techniques were used. The tool chosen for curve fitting was the open source online curve fitting and surface fitting tools provided at the website ZunZun.com [16] and it was found that, based on the criterion of lowest sum of squared absolute error, the best equation to fit the data was

$$THD = e^{a + \frac{b}{f_s} + c \ln f_s} + d \tag{7}$$

Hence, the relation was indeed exponential. The curves of the equation with the sets of coefficients that best fit the data are shown in Figs. 2–5.

Once again, for sampling frequency higher than 1000 Hz, the THD of the SVPWM design was much lower than that of the SVC design.

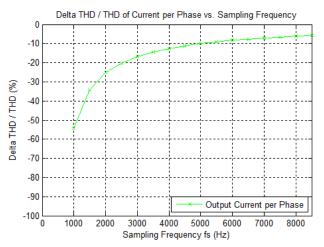

Fig. 7 Diagram of reduction in improvement to THD of current per phase vs. sampling frequency

As shown in Figs. 6 and 7, the relationship between the reduction to THD and the sampling frequency is inverse exponential. In other words, the relationship between the improvement to THD and the sampling frequency is also exponential. Thus, the improvement to THD diminishes as the sampling frequency increases. For instance, for the readings of current per phase, there is an almost 55% drop in the THD when the sampling frequency is increased from 500 Hz to 1000 Hz. That level of improvement is reduced to about 35% when the sampling frequency is further increased to 1500 Hz. That represents about 38% improvement to the previous increase in sampling frequency. This rate of improvement is about 20% when the sampling frequency is increased to 2500 Hz, and it is further reduced of approximately 50% when the sampling frequency reaches 5000 Hz. In other words, due to an inverse exponential decrease of THD with the increase of sampling frequency, the rate of improvement to the THD reduction is halved when the sampling frequency is doubled. That means the cost of further reducing THD goes exponentially as the sampling frequency is increased. Hence, in practice, there is bound to be a trade-off between the desired level of THD and the cost to achieve it. For instance, if 0.02 of THD is acceptable, then it is adequate to set the sampling frequency to 1000 Hz; and if 0.01 of THD is

tolerable, it is sufficient to set the sampling frequency to 2000 Hz; but if the THD has to be less than 0.05, then the sampling frequency has to be further increased to 4000 Hz.

#### VI. CONCLUSION

Several achievements of the investigation have been presented in this paper. Iterations of the design have been constructed with reducing numbers of independent parameters to show how most of the other parameters could be determined by the output frequency; even the sampling frequency could be set in relation to the output frequency. the limitation to the range of applicability of the model were identified and, using curve fitting techniques, it has been established that there is an exponential relation between the THD and the sampling frequency, as well as between the improvement in THD and the sampling frequency. Finally, its performance has been compared with that of the space vector control (SVC) design with the same sampling frequency, and it has been found that the performance of SVPWM is better than that of SVC with the same sampling frequency in most frequency range, including the range where the performance of the former is irregular.

Thus, the result of this investigation could be used as a gauge for the estimation of the types of components to be used for the desired output, or the outcome that could be expected with the components available. Currently, there is no indication of the optimal combination of parameters, as the actual costs of components have not yet been used in the investigation. However, it does indicate a way to get a set of predictable, acceptable and workable criteria for the desired results.

#### REFERENCES

- A. Kumar, K. Kumar, N. Kaushik, S. Sharma, and S. Mishra, "Renewable energy in India: Current status and future Potentials," *Renewable and Sustainable Energy Reviews*, Vol. 14, pp. 2434-2442, 2010.

- [2] S. N. Panchal, V. S. Sheth and A. A. Pandya, "Simulation Analysis of SVPWM Inverter Fed Induction Motor Drives," *International Journal of Emerging Trends in Electrical and Electronics*, Vol. 2, Is. 4, April 2013.

[3] Z. Shu, N. Ding, J. Chen H. Zhu and X. He, "Multilevel SVPWM with

- [3] Z. Shu, N. Ding, J. Chen H. Zhu and X. He, "Multilevel SVPWM with DC-Link Capacitor Voltage Balancing Control for Diode-Clamped Multilevel Converter Based STATCOM," *IEEE Transactions on Industrial Electronics*, Vol. 60, Is. 5, pp. 1884-1896, May 2013.

- Industrial Electronics, Vol. 60, Is. 5, pp. 1884-1896, May 2013.

[4] C. Xia, H. Shao, Y. Zhang, X. He, "Adjustable Proportional Hybrid SVPWM Strategy for Neutral-Point-Clamped Three-Level Inverters," *IEEE Transactions on Industrial Electronics*, Vol. 60 Is. 10, pp. 4234-4242, August 2012.

- [5] B. Gong, S. Cheng, Y. Qin, "Simple Three-Level Neutral Point Voltage Balance Control Strategy based on SVPWM," *Archives of Electrical Engineering*, Vol. 62, Is. 1, pp. 15–23, March 2013.

- [6] P. Chaturvedi and A. Dubey, "Analysis of Space Vector Pulse Width Modulation VSI Induction Motor on Various Conditions," *International Journal of Application or Innovation in Engineering & Management*, Vol. 2, Is. 12, pp. 409-414, December 2013.

- [7] M. Trzynadlowski, "An Overview of modern PWM Technologies for Three-Phase, Voltage-Controlled, Voltage-Source Inverters," *IEEE*, 1996

- [8] L. G. Franquelo, J. Rodríguez, J. I. Leon, Samir Kouro, Ramon Portillo, And M. A. M. Prats, "The Age of Multilevel Converters Arrives," *IEEE Industrial Electronics Magazine*. June 2008.

- [9] K. Zhou and D. Wang, "Relationship between Space-Vector Modulation and Three-Phase Carrier-Based PWM: A Comprehensive Analysis,"

- IEEE Transactions on Industrial Electronics, Vol. 49, Is. 1, February 2002.

- [10] D. Banupriya and K. S. S. Rani, "Total Harmonic Distortion Minimization in Induction Motor using Space Vector Modulation Scheme," *International Journal of Computer Applications* (0975 – 8887) Vol. 69, Is. 12, May 2013.

- [11] J. I. Leon, R. Portillo, L. G. Franquelo, S. Vazquez, J. M. Carrasco and E. Dominguez, "New Space Vector Modulation Technique for Single-Phase Multilevel Converters," IEEE International Symposium on Industrial Electronics, 2007, ISIE 2007.

- [12] R. Arulmozhiyal and K. Baskaran, "Space Vector Pulse Width Modulation Based Speed Control of Induction Motor using Fuzzy PI Controller," *International Journal of Computer and Electrical Engineering*, Vol. 1, Is. 1, April 2009.

- [13] E. Hendawi, F. Khater and A. Shaltout, "Analysis, Simulation and Implementation of Space Vector Pulse Width," Proceedings of the 9<sup>th</sup> WSEAS International Conference on Applications of Electrical Engineering, 2010.

- [14] P. B. Jyoti, J. Amarnath and D. Subbarayudu, "The Scheme of Three-Level Inverters based on SVPWM Overmodulation Technique for Vector Controlled Induction Motor Drives," *International Journal of Electrical Engineering & Technology*, Vol. 4, Is. 2, pp. 245-260, March-April 2013.

- [15] J. K. S. Ganesh, K. B. R. Uday and B. K. Babu, "SVPWM Based Step-Up Inverter," *International Journal of Engineering Research and Technology*, April 2013.

- [16] J. R. Phillips, Open Source Online Curve Fitting and Surface Fitting Web Site, ZunZun.com