ISSN: 2517-9438 Vol:2, No:5, 2008

# A Low Voltage High Performance Self Cascode Current Mirror

Jasdeep Kaur, Nupur Prakash, and S. S. Rajput

**Abstract**—A current mirror (CM) based on self cascode MOSFETs low voltage analog and mixed mode structures has been proposed. The proposed CM has high output impedance and can operate at  $\pm$  0.5 V. P-Spice simulations confirm the high performance of this CM with a bandwidth of 6.0 GHz at input current of 100  $\mu A$ .

*Keywords*—Current Mirrors, Composite Cascode Structure, Current Source/Sink.

## I. INTRODUCTION

MANY low voltage design techniques have been developed to meet the needs of present era of low power portable electronic equipment, which drove the analog designers to look for innovative design techniques like self cascode MOSFETs [1-5]. In this paper, we have investigated the merits and demerits of self cascode approach. For this aim in mind we designed a CM based on self cascode MOSFETs and analyzed its various properties through the p-spice simulations for 0.13 micron CMOS technology.

## II. CASCODE STRUCTURES

The idea behind cascode structure is to convert the input voltage to a current and apply the result to a common source stage. This has been employed in various LV topologies [6-10]. In 2004, Comer [11-12] discussed the effects on the overall composite cascode circuit performance with one device operating in the sub threshold and the other device operating in the active region and suggested that this approach may result in a very high gain stage for use in op-amps, along with low power dissipation too [13,14].

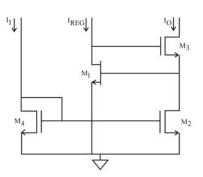

Fig. 1 Regulated cascode CM

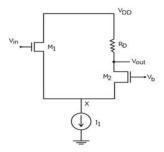

The idea of cascode structure is employed in regulated cascode [15,16] to increase the output resistance to  $g_m^2 r_{ds}^3$  (Fig. 1) and the implementation requires CMOS technology as the regulated cascode structure requires both PMOS and NMOS transistors. Fig. 2 is called "folded cascode", used to alleviate the drawback of telescopic cascode's, limited output swings and difficulty in shorting the input and output [16,17].

Primary advantage of folded structure lies in the choice of the voltage levels because it does not "stack" the cascade transistor on top of the input device. However, this structure generally consumes higher power.

Fig. 2 Folded cascade

The Composite Cascode Connection: It is seen that there are two distinct advantages of using cascode structures. Firstly, it provides higher output impedance and secondly, it reduces the effect of miller capacitance on the input of the amplifier. A Low Voltage Current Mirror (LVCM) based on level shifter approach was proposed that required a low bias voltage of order of  $\pm$  1.0V [18,19]. This paper proposes a LV high performance CM structure that applies composite cascode connections, proposed by Comer.

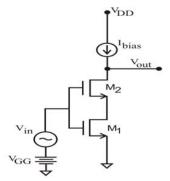

Fig. 3 Composite Cascode

ISSN: 2517-9438 Vol:2, No:5, 2008

The structure shown in Fig. 3, has both the gates of M1 & M2 driven by the input signal and share a single bias source  $V_{\rm GG}$ . If M2 and M1 have similar  $W\!/L$  ratio, then M1 will operate in the triode region while M2 will operate in the active region. In this case, the composite cascode works like a common-source stage, but with higher voltage gain. If M2 is chosen with higher aspect ratio then M1, with appropriate bias of  $V_{\rm GG}$  and  $I_{\rm bias}$ , M1 is placed in the strong inversion region while  $M_2$  is operating in the weak inversion region. The gain in this case is further increased.

Assuming the current source has infinite output impedance, the output resistance is  $r_{out} = r_{ds1} + r_{ds2} + (g_{m2} + g_{mb2}) r_{ds1} r_{ds2}$  [20]. The benefit of this conventional cascode technique is its high output impedance. Its drawbacks are limited input common mode range, small output swing and relatively high power supply requirements [21, 22].

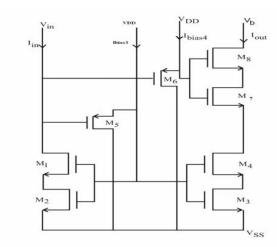

Fig. 4 Self Cascode LVCM

If this conventional cascode structure is changed to bias the upper MOS device  $M_2$  in a way that there is less effect on the output voltage swing, the output impedance of the connection may be increased with sufficient output swing at low supply voltage. One practice is to make both the gates of M1 & M2 driven by the input signal and share a single bias source. This approach results in high output impedance originating due to the degeneration of the source of M2. This composite cascode approach, which combines the regular active devices with weak inversion devices, is a promising low voltage design technique discussed in detail in this paper.

# Proposed Self cascode CM (SCLVCM):

The proposed LVCM is shown in Fig. 4. M1 & M2, M3 & M4, M7 & M8 are pairs of composite cascode structures. They have replaced M1, M2 & M3 of LVCM [19]. The aspect ratios of different transistors are given in Table I. The circuit is simulated for 0.13  $\mu$ m technology with level 3 parameters. Ibias3 and Ibias4 are assumed to be 1nA and 100 $\mu$ A respectively. The selection criterion for Ibias3 is to ensure lower V<sub>in.</sub> Ibias4 is selected to ensure ON condition for M6.

All the circuit operations are simulated for supply voltage of  $\pm$  0.5 V.

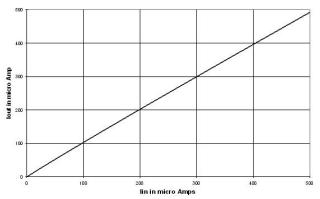

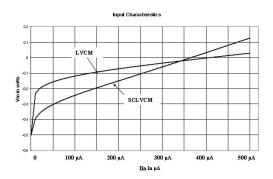

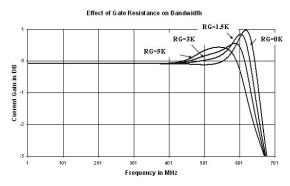

**Simulation Results:** The current transfer characteristics are shown in Fig. 5 and its input characteristics in Fig. 6. The effect of gate résistance over bandwidth is shown in Fig.7. The gate resistance RG is connected between the cascode pairs M1 & M2 and M3 & M4. For  $I_{\rm in}$  of 100  $\mu A$  the 3db bandwidth comes out to be 6.02 GHz. The bandwidth for  $I_{\rm in}$  of 250 $\mu A$  is 6.4 GHz and for  $I_{\rm in}$  of 300  $\mu A$  is 10.2 GHz. Thus bandwidth is shown to be a function of  $I_{\rm in}$ .

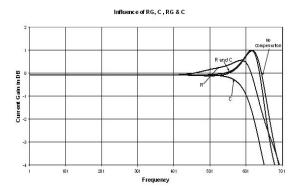

The influence of various compensation techniques over the bandwidth are shown in Fig. 8. The gate resistance of  $1.5 \mathrm{K}\Omega$  (RG) degrades the bandwidth from 6.02 GHz to 5.75 GHz and that of  $3 \mathrm{K}\Omega$  degrades it to 5.5 GHz. The capacitor (C) also degrades the bandwidth to 2.39 GHz. There is an improvement in bandwidth only when both Resistance and Capacitor are included, it comes out to be 4.7 GHz. Hence, for this structure the compensation techniques (RG and C) are not required.

Fig. 5 Current Transfer Characteristics

The small signal transfer analysis of this circuit at 100  $\mu A$  gave the current gain, i.e.  $I_{out}/$   $I_{in}=1,$  input resistance as  $1K\Omega$  and output resistance as 9  $M\Omega,$  with the power dissipation of 0.3 mW. However, for  $I_{in}$  of 300  $\mu A,$  the current gain changes to 0.9, input resistance to 900  $\Omega$  and output resistance to 2  $M\Omega.$

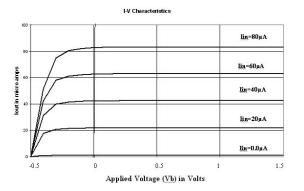

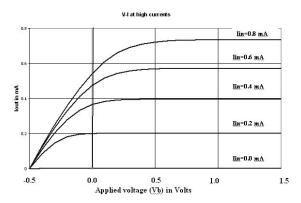

The power dissipation for this is 0.7 mW. The output current to applied drain bias characteristics of M8 ( $V_b$ ) is shown in Fig. 9 for the proposed self cascode LVCM of Fig. 4. Fig. 10 shows the characteristics for high currents. The dependency of output current swing on  $V_b$  is seen at low currents.

TABLE I W/L FOR VARIOUS TRANSISTORS

| W/L FOR VARIOUS TRANSISTORS |      |            |

|-----------------------------|------|------------|

| MOSFETS                     | TYPE | W/L(μm/μm) |

| M1,M4,M8                    | NMOS | 26/0.13    |

| M2,M3,M7                    | NMOS | 1.95/0.13  |

| M5,M6                       | PMOS | 1.95/0.13  |

ISSN: 2517-9438 Vol:2, No:5, 2008

Fig. 6 Input Characteristics of SCLVCM

Fig. 7 Effect of gate resistance over the bandwidth of SCLVCM

Fig. 8 Influence of RG and C, over the bandwidth of SCLVCM

Fig. 9 I-V Characteristics of proposed SCLVCM at low currents

Fig. 10 I-V Characteristics of proposed SCLVCM at high currents

### III. CONCLUSION

The self cascode LVCM presented here can be used as a high performance Current Sink and Source having an output resistance of 9 M $\Omega$ . This approach of increasing the (W/I) aspect ratios works effectively at low bias voltage  $V_{\rm in}$  of  $\pm$  0.5 V. Its high bandwidth (6.02 GHz) without any additional components makes it quite attractive for biasing analog circuits requiring high output resistance and gain. Hence can be used as load resistances in CM circuits. They can extensively be used where power supply requirements are not the constraint and that high output resistance is of utmost importance.

# REFERENCES

- X. Xie, M.C. Schneider, E. Sanchez-Sinencio, and S.H.K. Embabi, "Sound design of low power nested transconductance – capacitance compensation amplifiers," *Electronic letters*, Vol. 35, pp 956-958, June 1999.

- [2] Yan Shouli, Sanchez-Sinencio Edgar, "Low voltage Analog Circuit Design Techniques", *IEICE Transactions: Analog Integrated Circuits and Systems*, vol EOO +A, no.2, pp1-3, Feburary 2000.

- [3] G.Givstolisi, M. Conscione and F. Cutri, "A low-voltage low power voltage reference based on sub-threshold MOSFETs", *IEEE J. Solid*state circuits 38, pp-151-4, 2003.

- [4] S.S. Rajput and S.S. Jamuar, "Low voltage analog circuit design techniques", IEEE circuits systems Magazine 2, pp- 24-42, 2002

- [5] Alfonso Rincon M. Gabriel, "Low Voltage Design Techniques and Considerations for Integrated Operational Amplifier Circuit", Georgia Institute of Technology, Atlanta, GA, 30332, May 31, 1995.

- [6] A. Motsuzawa, "Low-Voltage and Low-Power Circuit Design for Mixed Analog / Digital Systems in Portable Equipment", *IEEE Journal of Solid-State Circuits*, Vol. 29 #4, pp. 470-480, April 1994.

- [7] R.L. Geiger, P.E. Allen, and N.R. Strader, VLSI Design Techniques for Analog and Digital Circuits. Me-Graw Hill: New York, 1990.

- [8] A. Zeki and H. Kuntman, "Accurate and high output impedance current mirrors suitable for CMOS current output stages." *Electron. Lett.*, vol. 33, pp. 1042–1043, 1997.

- [9] S.S. Rajput and S.S. Jamuar, "Current mirrors: Essential units for analog circuit structures." *IETE J. of Education*, vol. 4.3, no. 4, 2002.

- [10] S.S. Rajput and S.S. Jamuar, "Low voltage, low power high performance current mirror for portable analogue and mixed mode applications." In *Proc. IEE—Circuits Devices and Syst*, 2001, vol. 148, no. 5 pp. 273– 278.

- [11] D.J. Comer and D.T. Comer, Fundamentals of electronic circuit design. New York: John Wiley & sons Inc. 2003

#### International Journal of Electrical, Electronic and Communication Sciences

ISSN: 2517-9438 Vol:2, No:5, 2008

- [12] D.J. Comer and D.T. Comer, and C.petrie, "The utility of the composite cascade in analog CMOS design," *International Journal of Electronics*, vol.91,no.8, pp.491-502, Aug.2004.

- [13] P.Gray and R. Meyerce, Analysis and design of analog integrated circuits. New York: John Wiley & sons, 1977

- [14] V.I. Proddanov and M.M. Green, "CMOS current mirrors with reduced input and output voltage requirements." *Electron. Lett.*, vol. 32, pp. 104– 105, 1996.

- [15] J. Millman and A. Grabel, "Microelectronics", New York: Mc Graw-Hill 1987.

- [16] P.E. Allen and D.R. Holberg, CMOS Analog Circuit Design, Holt, Rinehart and Winston, Inc.: New York, 1987.

- [17] J. Ramirez-Angulo, "Low voltage current mirrors for built in current sensors." ISCAS-1994/IEEE, pp. 529–532, 1994.

- [18] S.S. Rajput, "Low voltage current mode circuit structures and their applications." Ph.D. Thesis, Indian Institute of Technology, Delhi, 2002.

- [19] S.S. Rajput and S.S. Jamuar, "A current mirror for low voltage, high performance Analog Circuits." In *Proc. Analog integrated Circuits & Signal, Kluwer Academic Publications*, 36, pp. 221-233, 2003.

- [20] T. Itakura and Z. Czarnul, "High output resistance CMOS current mirrors for low voltage applications." *IEICE Trans. Fundamentals*, vol. E80-A, no. 1, pp. 230–232, 1997.

- [21] J. Mulder, A.C. Woerd, W.A. Serdijn, and A.H.M. Roermund, "High swing cascode MOS current mirror." *Electron. Lett.*, vol. 32, pp. 1251– 1252, 1996.

- [22] E. Sackinger and W. Guggenbuhl, "A high swing, high impedance MOS cascode current mirror." *IEEE J. Solid State Circuits*, vol. 25, pp. 289– 298, 1990.

Jasdeep Kaur received her B.E. (1996), M.E.(2003) in Electronics & Communication from Delhi College of Engineering. She joined Netaji Subhas Institute of Technology (1996-2000) as Technical Officer and worked extensively for Govt. aided Continuing Education Programme(CEP) and Special Component Programme(SCP). She joined Guru Tegh Bahadur Institute of Technology (affiliated to GGS Indraprastha University) and was instrumental in establishing ECE Deptt. She is a Life member of ISTE and IETE. Her areas of interests include Low voltage Low Power Designs and Digital circuits. She has several National Publications to her credit and has guided several under graduate projects too.

Nupur Prakash is working as Dean and Professor in the University School of Information Technology. Prior to this she was Principal of Indira Gandhi Institute of Technology, a constituent college of GGS Indraprastha University and a girl's engineering college started by Govt. of Delhi for four years (2002-06). She joined GGS Indraprastha University as Professor in IT in 2001. She received her B.E. (Electronics & Communication Engineering) and M.E. (Computer Science & Technology) from University of Roorkee (now I.I.T. Roorkee) in 1981 and 1986 respectively. She was awarded with the Chancellor's Medal for being the best outgoing student of 1981. She has worked as a scientist in CSIO, Chandigarh (1983-85) on microprocessor based projects. She completed her PhD (Computer Engineering & Technology) from Punjab University, Chandigarh in 1998 in the area of Neural Networks and Natural language Processing.

S. S. Rajput has received his B. E. in Electronics and Communication Engineering and M. E. in Solid State Electronics Engineering from University of Roorkee, Roorkee, India (Now IIT, Roorkee) and was awarded University gold medal. He earned his Ph. D. degree from Indian Institute of Technology, Delhi. He joined National Physical Laboratory, New Delhi, India as Scientist B, and was Scientist F when he moved to ABV-IIITM Gwalior as professor. He has worked for the design, development, testing and fabrication of an instrument meant for space exploration under the ISRO-NPL joint program for development of scientific instruments for the Indian Satellite SROSS-C and SROSS-C2 missions. His research interests include low voltage analog VLSI and instrument design for space applications. He has chaired the many sessions in Indian as well as International conferences. He is Fellow member of IETE (India). He has been awarded best paper award for IETE Journal of Education for the year 2002. He is Associate Editor of International Journal of Electronics UK, and Editorial Board member of Journal of Active and Passive

Electronic Devices USA and Journal of Programmable Devices, Circuits, and Systems (PDCS), Egypt. Few tutorials have been presented in International Conferences on his Research Work. He has more than 60 publications in national and international journals and conferences including a book chapter.