# The Excess Loop Delay Calibration in a Bandpass Continuous-Time Delta Sigma Modulators Based on Q-Enhanced LC Filter

Sorore Benabid

Abstract—The Q-enhanced LC filters are the most used architecture in the Bandpass (BP) Continuous-Time Delta-Sigma ( $\Sigma\Delta$ ) modulators, due to their: high frequencies operation, high linearity than the active filters and a high quality factor obtained by Q-enhanced technique. This technique consists of the use of a negative resistance that compensate the ohmic losses in the on-chip inductor. However, this technique introduces a zero in the filter transfer function which will affect the modulator performances in term of Dynamic Range (DR), stability and in-band noise (Signal-to-Noise Ratio (SNR)). In this paper, we study the effect of this zero and we demonstrate that a calibration of the excess loop delay (ELD) is required to ensure the best performances of the modulator. System level simulations are done for a 2<sup>nd</sup> order BP CT ( $\Sigma\Delta$ ) modulator at a center frequency of 300MHz. Simulation results indicate that the optimal ELD should be reduced by 13% to achieve the maximum SNR and DR compared to the ideal LC-based  $\Sigma\Delta$  modulator.

Keywords—Continuous-time bandpass delta-sigma modulators, excess loop delay, on-chip inductor, Q-enhanced LC filter.

### I. INTRODUCTION

${f B}$  ANDPASS (BP) continuous-time (CT) delta-sigma (\$\Sigma\$) modulators are a popular architecture for a high resolution and a high speed analog-to-digital converter (ADC). The CT second-order filter (or resonator) is the fundamental building block in the BP CT  $\Sigma\Delta$  modulators to provide the sufficient selectivity. The resonators can be implemented by on-chip LC tank circuits because of their simple structure and their high linearity compared to transconductance-capacitor (Gm-C) filters [1], [2]. However, the on-chip Q-factor of the inductors is typically less than 10, limited due to the considerable ohmic losses [3]. The Q-enhanced technique using a negative resistance is the most used method to compensate these losses. Though, this technique will introduce a zero in the filter transfer function and will affect the Dynamique Range (DR), the Signal-to-Noise Ratio (SNR) and the stability of the modulator. Consequently, we propose in this paper to study the effect of the zero of the Q-enhanced LC filter transfer function and we will demonstrate that a calibration of the excess loop delay (ELD) is required to preserve the modulator performances.

The paper is organized as follows: The modulator architecture and system considerations are reported in Section II, while the Q-enhanced LC resonator are developed in Section III. The ELD is presented in Section IV. The

Sorore Benabid is with the Department of Electronics, Polytechnic Institute of Advanced Sciences, Ivry-sur-Seine, France (e-mail: sorore.benabid@ipsa.fr).

simulation results are discussed in Section V. Finally, concluding remarks are given in Section VI.

# II. MODULATOR ARCHITECTURE AND SYSTEM CONSIDERATIONS

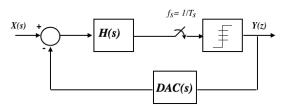

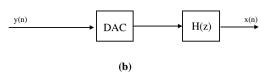

The general block diagram of a BP CT  $\Sigma\Delta$  modulator is depicted in Fig. 1. It consists of a CT loop filter H(s)whose output will be sampled by the quantizer at frequency  $f_s$  [2]. It is usually preferred to make  $f_s$  four times the input frequency  $f_0$  to simplify the design of the down-sampling mixer at the modulator output. The quantizer will produce a discret time (DT) output signal which is fed back through a digital-to-analog converter (DAC) expressed by the transfer function (DAC(s)). A non-return-to-zero (NRZ) DAC pulse is used in the feedback path as it minimizes the clock jitter effects than a return-to-zero (RZ) or a halfway-return-to-zero (HRZ) DAC pulse. The design starts by fixing the modulator specifications (loop filter order, the quantizer resolution and the oversampling ratio (OSR)) to achieve the required DR and SNR. In this work, we will focus on the system level design of a  $2^{nd}$  order BP CT  $\Sigma\Delta$  modulator with 1-bit quantizer and integrated LC resonator. We will discuss the technique to compensate the finite quality factor of the on-chip inductor while preserving the modulator's performances.

Fig. 1 Block diagram of the CT  $\Sigma\Delta$  modulator

#### III. Q-ENHANCED LC RESONATOR

The LC resonator is the most important block in the loop filter of the BP CT  $\Sigma\Delta$  modulator because it must provide a sufficient selectivity at the intermediate frequency (IF) of operation before the signal is sampled by the quantizer. In this section, we study two cases of LC resonator: the ideal case with ideal inductor (with high quality factor) and the real case taking into account the losses in the inductor which reduce the filter quality factor and therefore the modulator resolution.

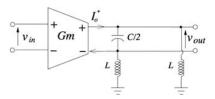

Fig. 2 represents the ideal LC resonator composed by a transconductance stage  $(G_m)$  that transfer the input voltage  $(v_{in})$  into current which is then injected into the ideal LC tank.

Fig. 2 Ideal LC resonator

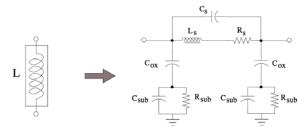

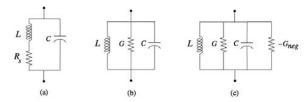

For the second case, we consider the real on-chip inductor taking into account the parasitics as represented in the equivalent model of Fig. 3. The serial resistance  $R_s$  constitue the dominant losses which has been replaced by a parallel conductance G as shown in Fig. 4 (b). This conductance depends of the inductor quality factor  $(Q_{ind})$  and  $R_s$  as indicated by 1. The conductance G should be compensate by a negative conductance  $(-G_{neg})$  as depicted in Fig. 4 (c). Therefore, the resonator quality factor may increase by adjusting  $-G_{neg}$  while preserving the stability condition  $(G_{neg} < G)$ .

$$G = \frac{1}{(Q_{ind}^2 + 1)R_s} \tag{1}$$

Fig. 3 Equivalent model of the on-chip inductor

Fig. 4 (a) LC cell with ohmic losses. (b) Equivalent Circuit to (a) near resonant frequency. (c) Q-enhancement using negative resistance

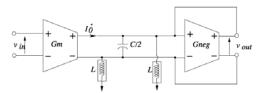

As a result, we obtain the  $2^{nd}$  order Q-enhanced LC filter (Fig. 5) which consists in a gain stage  $(G_m)$ , a parallel LC tank and the cross-coulped transconductor  $(G_{neg})$  that operate as a negative resistance.

Table I reports the equations of the LC resonator transfer function H(s) [4], central pulsation  $\omega_0$  and the ratio  $\omega_0/Q$  for the ideal and real case. As we can see, in the real case, the difference  $R_s/L - G_{neg}/C$  will be reduced by adjusting  $G_{neg}$

Fig. 5 Q-enhanced LC resonator

and consequently the resonator quality factor will be improved. In the other hand, we can notice that a zero ( $\alpha = R_s/L$ ) appears in the resonator transfer function H(s). This zero will affect the performances and the stability of the modulator. We will discuss in the next sections the effect of this zero and how we will compensate its impact.

#### IV. EXCESS LOOP DELAY

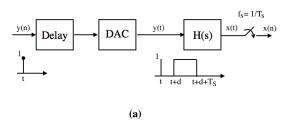

The one of major concerns of CT  $\Sigma\Delta$  modulators is the ELD. The ELD (d) indicates the delay between the quantizer clock and the DAC output due to the transistors switching time in the quantizer and the DAC [5]. We illustrate in Fig. 6 the open-loop diagram of the  $\Sigma\Delta$  modulator in the both cases CT and DT to explain the equivalent DT loop filter H(z) for a given CT loop filter H(s). A CT and DT modulator would produce the same sequence of output bits y(n) if the inputs to the quantizer x(n) in each were identical at the sampling instants  $(t = nT_s)$ . As indicated in previous section, we consider NRZ DAC in which the output pulse remains constant over a full period.

Fig. 6 Open-loop  $\Sigma\Delta$  modulator (a) CT (b) its equivalent DT

The impulse responses of the open-loop diagrams in Fig. 6 were equal at sampling times, leading to the well-known equivalence called the impulse-invariant transformation [5], [6], [2]:

$$H(z) = Z[L^{-1}[H(s).DAC(s)]]$$

(2)

where Z and L denote the Z-transform and L-transform symbols, respectively. As referred in [6], [7], the expression of the NRZ DAC with delay  $d = \tau T_s$  is,

TABLE I LC RESONATOR TRANSFER FUNCTION

| Architecture            | H(s)                                                                                                                                    | $\omega_0$                               | $\omega_0/Q$                        |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------|

| Ideal LC resonator      | $\frac{G_m}{C} \cdot \frac{s}{s^2 + 1/LC}$                                                                                              | $\frac{1}{\sqrt{LC}}$                    | 0                                   |

|                         | $=A.\frac{s}{s^2+\omega_0^2}$                                                                                                           |                                          |                                     |

| Real LC resonator using | $\frac{G_m}{C} \cdot \frac{s + R_s/L}{s^2 + \left(\frac{R_s}{L} - \frac{G_{neg}}{C}\right)s + \frac{1}{LC}\left(1 - G_{neg}R_s\right)}$ | $\frac{1}{\sqrt{LC}}\sqrt{1-G_{neg}R_s}$ | $\frac{R_s}{L} - \frac{G_{neg}}{C}$ |

| a Q-enhanced technique  | $=A.\frac{s+\alpha}{s^2+\frac{\omega_0}{Q}+\omega_0^2}$                                                                                 |                                          |                                     |

|                         | $\simeq A.\frac{s+lpha}{s^2+\omega_0^2}\mid_{Q\simeq\infty}$                                                                            |                                          | $\simeq 0$                          |

$$DAC(s) = \frac{e^{-\tau T_s s} - e^{-(1+\tau)T_s s}}{s}$$

(3)

Based on the transfer function of the Q-enhanced LC resonator given in Table I, and according to the equation of the NRZ DAC with delay (3), the loop filter in the Z-domain (2) would be:

$$H(z) = Z \left\{ L^{-1} \left[ A \cdot \frac{s + \alpha}{s^2 + \omega_0^2} \cdot \frac{e^{-\tau T_s s} - e^{-(1+\tau)T_s s}}{s} \right] \right\}$$

$$= (1 - z^{-1}) Z \left\{ L^{-1} \left[ A \cdot \frac{s + \alpha}{s^2 + \omega_0^2} \cdot \frac{e^{-\tau T_s s}}{s} \right] \right\}$$

$$= (1 - z^{-1}) \underbrace{\left\{ Z \left\{ L^{-1} \left[ A \cdot \frac{s}{s^2 + \omega_0^2} \cdot \frac{e^{-\tau T_s s}}{s} \right] \right\} \right\}}_{1}$$

$$+ (1 - z^{-1}) \underbrace{\left\{ Z \left\{ L^{-1} \left[ A \cdot \frac{\alpha}{s^2 + \omega_0^2} \cdot \frac{e^{-\tau T_s s}}{s} \right] \right\} \right\}}_{1}$$

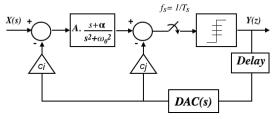

Most previous works have proposed some solutions to compensate the ELD in CT  $\Sigma\Delta$  modulators ignoring the term II (4), this by considering negligible the  $s^0$  term in the numerator of H(s) ( $\alpha=0$ ) [8], [9]. One of these solutions consists to an additional feedback path as shown in Fig. 7, by demonstrating that the optimal delay is included between  $1.4.T_s$  and  $1.8.T_s$  to ensure stability and the best performances. However, the  $s^0$  term in the numerator of H(s) should be considered and can not be removed ( $\alpha \neq 0$ ), as mentioned previously in table I, because it depends directly of the on-chip inductor ( $R_s/L$ ). Therefore, in this work, we propose to calibrate loop delay ( $d=\tau T_s$ ) and therefore decrease the impact of the term II (4) in order to achieve the performances as close as possible to the ideal case.

Fig. 7 Block diagram of the  $2^{nd}$  order BP CT  $\Sigma\Delta$  modulator with ELD

#### V. SIMULATION RESULTS

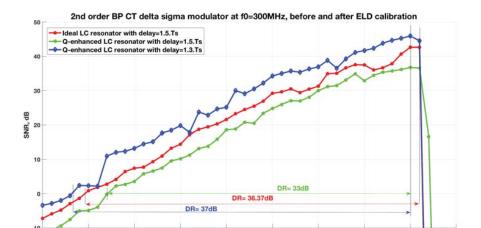

The system level simulations of the  $2^{nd}$  order BP CT  $\Sigma\Delta$  modulator was done in Matlab environment. The input signal is a sine wave at 300MHz and a sampling frequency  $f_s = 1.2GHz$  with an OSR of 64. Fig. 8 shows the simulation results of the SNR in function of input magnitude in three different cases. The first result exhibited by the red line corresponds to the modulator with ideal LC resonator and a delay  $d = 1.5.T_s$ . The result indicated by green line shows the modulator with a real LC resonator based on Q-enhanced technique with the same delay ( $d = 1.5.T_s$ ). As we can see, the SNR and DR decreased respectively by about 6dB and 3.37dB compared to the ideal case. This difference is due to the zero in the Q-enhanced LC filter transfer function ( $\alpha \neq 0$  in 4). To reduce the zero effect, we reduced the delay  $(d = 1.3.T_s)$ and the result illustrated by the blue line shows that the DR is approximatively equal to the ideal case (37dB) and there is an improvement on SNR about 4dB ( $SNR_{max} = 46dB$ ).

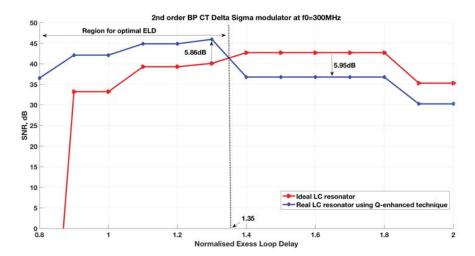

Furthermore, the modulator was simulated for different delay in the two previous cases (ideal and real case) and the maximum SNR for each delay was recorded as shown in Fig. 9. As we can see, the maximum SNR decreased by 5.95dB compared to the ideal case when  $d > 1.35T_s$ . Consequently, the delay should be calibrate lower than  $1.35T_s$  to compensate these decrease and the maximum SNR is achieved at  $d = 1.3T_s$ . It can be also noticed that the Q-enhanced LC resonator makes it possible to have a wider ELD interval compared to the ideal case.

## VI. CONCLUSION

The most critical limitation in LC-based BP CT  $\Sigma\Delta$  modulators is the finite quality factor of integrated inductor due to the ohmic losses. To compensate these losses, the Q-enhanced technique employing a negative resistance is commonly used. However, a  $s^0$  term in the numerator of the Q-enhanced LC resonator transfer function will be introduced. In this paper we have studied the effect of this term and how it will affect the performance of the BP CT  $\Sigma\Delta$  modulator. The behaviour was verified through the system level design of a  $2^{nd}$  order BP CT  $\Sigma\Delta$  modulator with NRZ feedback DAC and a  $2^{nd}$  order Q-enhanced LC resonator at  $f_0 = 300MHz$ . Simulation results show that calibrating the ELD can greatly mitigate the performance loss due to the  $s^0$  term.

Fig. 8 SNR vs. input amplitude for a  $2^{nd}$  order BP CT  $\Sigma\Delta$  in two cases: with an ideal and a real LC resonator, before and after ELD calibration

Input, dB

Fig. 9 Maximum SNR vs. ELD for a  $2^{nd}$  BP CT  $\Sigma\Delta$  in two cases: using an ideal and a real LC resonator

# ACKNOWLEDGMENT

The author would like to thank Mr Tamer Badran PhD student in the System On Chip (SOC) department at University Pierre et Marie Curie (UPMC) for his technical support.

#### REFERENCES

- [1] S. Gupta, D. Gangopadhyay, H. Lakdawala, J. C. Rudell, and D. J. Allstot, "A 0.8-2 GHz fully-integrated QPLL-timed direct-RF-sampling bandpass ΣΔ ADC in 0.13 μm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 5, pp. 1141–1153, May 2012.

- [2] G. Molina-Salgado, A. Morgado, G. J. Dolecek, and J. M. de la Rosa, "LC-based bandpass continuous-time sigma-delta modulators with widely tunable notch frequency," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 61, no. 5, pp. 1442–1455, May 2014.

- [3] J. Lota and A. Demosthenous, "Q-enhancement with on-chip inductor optimization for reconfigurable ΔΣ radio-frequency ADC," in 2015 IEEE 13th International New Circuits and Systems Conference (NEWCAS), June 2015, pp. 1–4.

- [4] G. M. Salgado, G. J. Dolecek, and J. M. de la Rosa, "On the use of passive circuits to implement LC-based band-pass CT ΣΔ modulators," in 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS), Aug 2015, pp. 1–4.

- [5] J. A. Cherry and W. M. Snelgrove, "Excess loop delay in continuous-time delta-sigma modulators," *IEEE Transactions on Circuits and Systems II:* Analog and Digital Signal Processing, vol. 46, no. 4, pp. 376–389, Apr 1999

- [6] S. Loeda, H. M. Reekie, and B. Mulgrew, "On the design of high-performance wide-band continuous-time sigma-delta converters using numerical optimization," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 53, no. 4, pp. 802–810, April 2006.

[7] C.-Y. Cai, Y. Jiang, S.-W. Sin, S.-P. U, and R. P. Martins,

- [7] C.-Y. Cai, Y. Jiang, S.-W. Sin, S.-P. U, and R. P. Martins, "Excess-loop-delay compensation technique for CT ΣΔ modulator with hybrid active–passive loop-filters," Analog Integrated Circuits and Signal Processing, vol. 76, no. 1, pp. 35–46, Jul 2013. [Online]. Available: https://doi.org/10.1007/s10470-013-0069-z

- [8] A. Yahia, P. Benabes, and R. Kielbasa, "The influence of the feedback DAC delay in continuous-time bandpass DS converters," May 2001, pp. 716–719.

- [9] A. Ashry and H. Aboushady, "Using excess loop delay to simplify LC-based ΣΔ modulators," *Electronics Letters*, vol. 45, no. 25, pp. 1298–1299, December 2009.