# An Improved Design of Area Efficient Two Bit Comparator

Shashank Gautam, Pramod Sharma

Abstract—In present era, development of digital circuits, signal processors and other integrated circuits, magnitude comparators are challenged by large area and more power consumption. Comparator is most basic circuit that performs comparison. This paper presents a technique to design a two bit comparator which consumes less area and power. DSCH and MICROWIND version 3 are used to design the schematic and design the layout of the schematic, observe the performance parameters at different nanometer technologies respectively.

**Keywords**—Chip design, consumed power, layout area, two bit comparator.

## I. INTRODUCTION

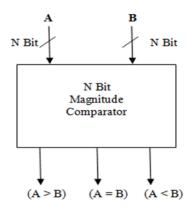

COMPARATOR is commonly known as amplitude or magnitude comparator. Magnitude comparator is a combinational logic circuit and is very useful and basic circuitry that performs comparison in digital devices such as signal processors (DSP) and microprocessors [1]. Basically, comparator is a logic circuit which is able to compare the magnitude of the input lines and provides the corresponding result at the output. The output obtained is basically the relation between the two numbers i.e. (less than, greater than, equal to) (Fig. 1).

Fig. 1 Block diagram of N bit magnitude comparator

Shashank Gautam is pursuing his Master of Technology degree in Electronics and Communication from Dr. A.P.J. Abdul Kalam Technical University, Lucknow, India. (e-mail: shashankgautam92@gmail.com).

Pramod Sharma is currently working as an assistant professor in the department of Electronics & Communication Engineering, Raja Balwant Slingh Engineering Technical Campus, Bichpuri, Agra, Uttar Pradesh, India. (e-mail: pdsharma\_rbs@yahoo.co.in).

#### II. TWO BIT MAGNITUDE COMPARATOR

Two bit magnitude comparator is a combinational logic circuit. This circuit has three output lines i.e. (A less than B), (A greater than B) and (A equal to B). For this type of arrangement truth table consists of four inputs variables and sixteen entries as shown in Table I [2], [3].

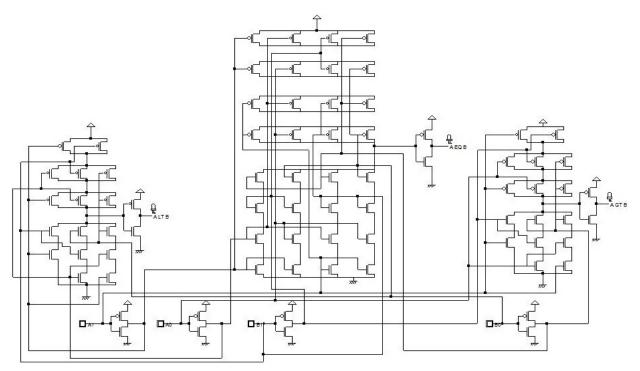

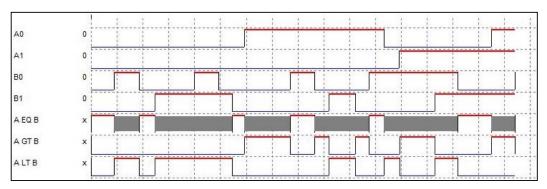

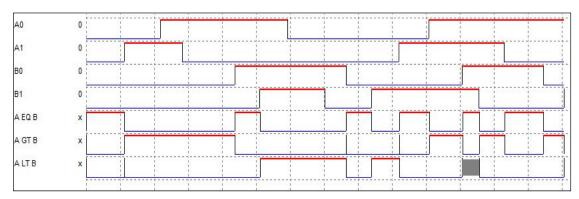

Table I provides the output state for every possible value of input of two bit magnitude comparator. Truth table of two bit comparator was simplified using K-map and obtained equations were used to design the circuit of two bit comparator with CMOS logic. Fig. 2 shows the circuit diagram of two bit magnitude comparator designed with the help of CMOS technology. Fig. 3 shows the waveform diagram of two bit magnitude comparator showing different states of inputs and outputs [4].

## III. PROPOSED APPROACH

Using technique described in this paper, an area efficient layout of two bit magnitude comparator is designed. In the approach, we prepare two different tables for both (A<B) and (A=B).

## A. Occurrence for A<B

Using the truth table of two bit comparator four situations can be derived. Using these four conditions, circuit for (A<B) can be designed:

- If A1 = 0 = A0; (A < B) = B1 + B0

- If A1 = 0 and A0 = 1; (A < B) = B1

- If A1 = 1 and A0 = 0; (A < B) = B1.B0

- If A1 = 1 = A0; (A < B) = 0

Conditions derived for (A<B) clearly describe that for

(A<B) we make use of one AND logic gate and one OR logic gate and hence less number of transistors will be used.

Fig. 2 Two bit magnitude comparator circuit by CMOS approach

Fig. 3 Two bit magnitude comparator circuit waveform diagram

TABLE II CEARRANGED TRUTH TABLE FOR A=B

| REARRANGED TRUTH TABLE FOR A=B |                |       |       |       |  |  |

|--------------------------------|----------------|-------|-------|-------|--|--|

| $A_0$                          | $\mathrm{B}_0$ | $A_1$ | $B_1$ | A = B |  |  |

| 0                              | 0              | 0     | 0     | 1     |  |  |

| 0                              | 1              | 0     | 0     | 0     |  |  |

| 0                              | 0              | 0     | 1     | 0     |  |  |

| 0                              | 1              | 0     | 1     | 0     |  |  |

| 1                              | 0              | 0     | 0     | 0     |  |  |

| 1                              | 1              | 0     | 0     | 1     |  |  |

| 1                              | 0              | 0     | 1     | 0     |  |  |

| 1                              | 1              | 0     | 1     | 0     |  |  |

| 0                              | 0              | 1     | 0     | 0     |  |  |

| 0                              | 1              | 1     | 0     | 0     |  |  |

| 0                              | 0              | 1     | 1     | 1     |  |  |

| 0                              | 1              | 1     | 1     | 0     |  |  |

| 1                              | 0              | 1     | 0     | 0     |  |  |

| 1                              | 1              | 1     | 0     | 0     |  |  |

| 1                              | 0              | 1     | 1     | 0     |  |  |

| 1                              | 1              | 1     | 1     | 1     |  |  |

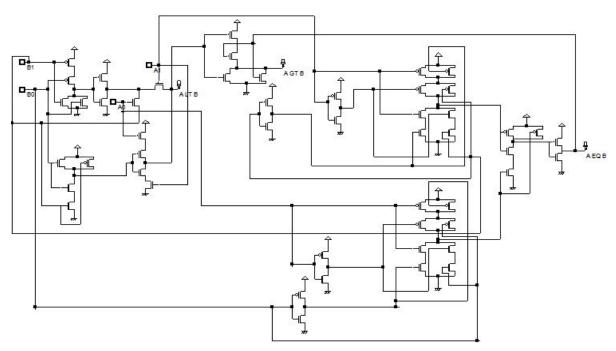

Fig. 4 Two bit comparator circuit using presented technique

Fig. 5 Waveform diagram of two bit comparator designed using presented technique

# B. Occurrence for A=B

To determine the occurrence for (A=B), we rearrange the inputs of the truth table of two bit magnitude comparator as shown in Table II. From Table II, we can easily derive the states for (A=B)

- If A0 = B0; (A = B) = A1 (EXNOR) B1

- If (A0=0 and B0=1) or (A0=1 and B0=0); (A=B)=0

It is very clear from the occurrence that circuit for (A = B) will be made by two EXNOR logic gates and require less number of transistors.

# C. Occurrence for A>B

For acquiring the result for (A>B), NOR function is utilized. NOR operation is performed on the two obtained outputs. It is evident from the conditions for (A<B), (A=B), (A>B) will use minimum transistor count hence an area efficient two bit magnitude comparator can be designed using described approach.

The circuit diagram of two bit magnitude comparator designed using presented technique is shown in Fig. 4. It is evident from the circuit diagram of two bit magnitude comparator designed by both approaches that two bit magnitude comparator designed by presented technique comprises of less number of transistors than magnitude comparator designed by using preexisting CMOS logic approach. Fig. 5 shows the waveform of two bit magnitude comparator designed using presented approach. It can be concluded from the figure that comparator designed using presented work gives same results as the previous one.

# IV. LAYOUT DESIGNING

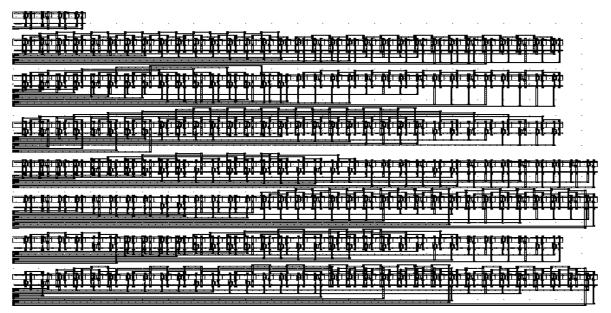

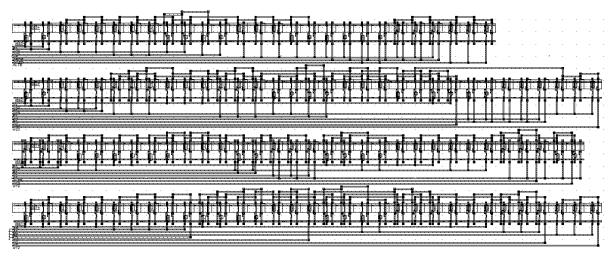

Designing the layout of the circuit previously developed using CMOS approach and presented technique is a significant part of the research work since all the results related to power consumed and area consumed by the circuit can only be done on the fabricated layout of the two bit comparator. After

designing the circuit or schematic on DSCH (Data Schematic version 2) it is being tested and verified according to the truth table. Further, MICROWIND version 3.1 is used to develop

the layout and is being analyzed on different technologies which are 90 nm, 65 nm, 45 nm and 32 nm [5].

Fig. 6 Layout of two bit comparator designed using CMOS approach at 90 nm technology

Fig. 7 Layout of two bit comparator designed using CMOS approach at 65 nm technology

Vol:10, No:11, 2016

Fig. 8 Layout of two bit comparator designed using CMOS approach at 45 nm technology

Fig. 9 Layout of two bit comparator designed using CMOS approach at 32 nm technology

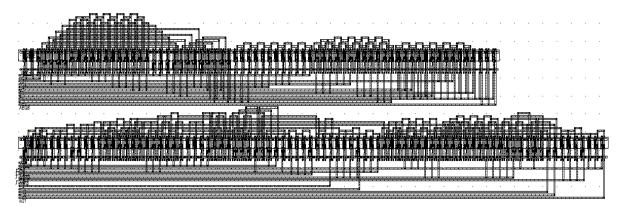

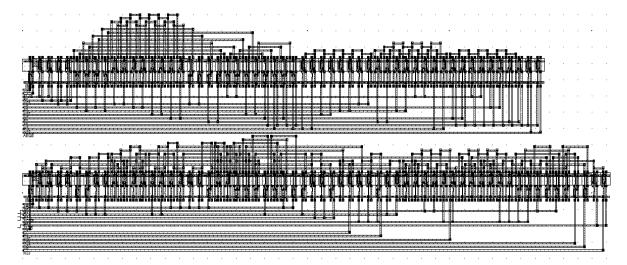

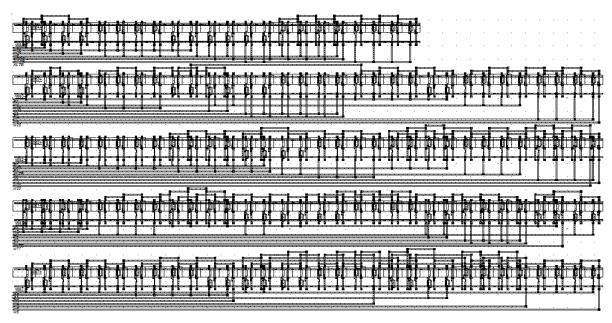

Layout of two bit comparator designed using CMOS approach at 90 nm is shown in Fig. 6. Layout of two bit

comparator designed using CMOS approach at 65 nm is shown in Fig. 7. Layout of two bit comparator designed using

CMOS approach at 45 nm is shown in Fig. 8. Layout of two bit comparator designed using CMOS approach at 32 nm is shown in Fig. 9. Further, these layouts were analyzed for on chip area and consumed power.

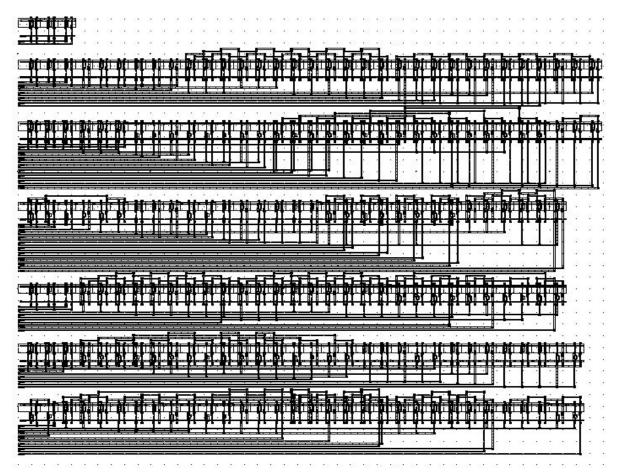

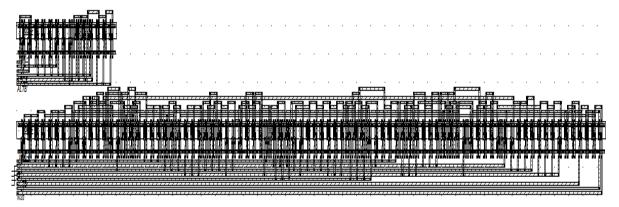

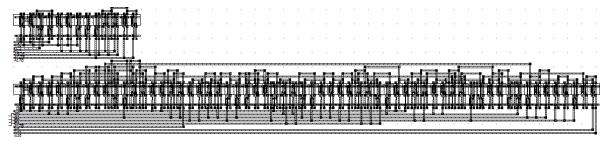

Fig. 10 shows the layout of the two bit magnitude comparator designed using presented approach as stated in this paper and fabricated at 90 nm technology. Layout of two bit comparator designed using presented approach at 65 nm is

shown in Fig. 11. Layout of two bit comparator designed using presented approach at 45 nm is shown in Fig. 12. Layout of two bit comparator designed by making use of presented approach at 65 nm technology is depicted in Fig. 13. Further, these layouts were also analyzed and simulated for calculation of on chip area and power consumption so that a comparative study can be done.

Fig. 10 Layout of two bit comparator designed by presented approach at 90 nm technology

Fig. 11 Layout of two bit comparator designed by presented approach at 65 nm technology

Fig. 12 Layout of two bit comparator designed by presented approach at 45 nm technology

ISSN: 2517-9438

Vol:10, No:11, 2016

Fig. 13 Layout of two bit comparator designed by presented approach at 32 nm technology

#### V.RESULT AND DISCUSSION

Comparator designed by CMOS approach requires 78 transistors while designing of the circuit using presented approach makes use of only 50 transistors which is a remarkable reduction in transistor count. Layout structure of the circuits is designed and fabricated at various nm technologies. Analysis is done at BSim4 level and operating temperature is taken as 27 °C. Results for both the approaches were compared.

Comparative results of power consumption for both approaches are shown in Table III. Comparative results of area consumption for both approaches are shown in Table IV.

TABLE III POWER CONSUMED BY BOTH TECHNIQUES

| TOWL  | TOWER CONSCINED BY BOTH TECHNIQUES |                     |  |  |  |

|-------|------------------------------------|---------------------|--|--|--|

|       | CMOS                               | Presented Technique |  |  |  |

| 90 nm | 73.24 μW                           | 229.0 μW            |  |  |  |

| 65 nm | 13.72 μW                           | 39.96 μW            |  |  |  |

| 45 nm | $0.030 \mu\mathrm{W}$              | 0.039 μW            |  |  |  |

| 32 nm | 0.025 μW                           | 0.029 μW            |  |  |  |

TABLE IV AREA CONSUMED BY BOTH TECHNIQUES

| AREA CONSUMED BY BOTH TECHNIQUES |                        |                        |  |  |

|----------------------------------|------------------------|------------------------|--|--|

|                                  | CMOS                   | Presented Technique    |  |  |

| 90 nm                            | 2644.1 μm <sup>2</sup> | 1686.4 μm²             |  |  |

| 65 nm                            | 1853.3 μm <sup>2</sup> | $1130.2  \mu m^2$      |  |  |

| 45 nm                            | 2561.1 μm <sup>2</sup> | 1323.1 μm <sup>2</sup> |  |  |

| 32 nm                            | $1738.1  \mu m^2$      | 961.9 μm²              |  |  |

## VI. CONCLUSION

Two bit magnitude comparator designed using presented approach is found to be much more efficient from comparator designed by CMOS approach. The chip area and power consumed by two bit comparator is reduced and minimized to a very large extent using different nanometer technologies. On chip area of presented circuit comes out to be 44.66% less than the circuit designed by CMOS approach. Power consumption of comparator designed by CMOS technique and presented technique is nearly same.

#### REFERENCES

- [1] Morgenshtein, A.; Fish, A.; Wagner, I.A., "Gate-diffusion input (GDI): A Power efficient method for digital combinational circuits," IEEE Transaction on Very Large Scale Integration (VLSI) Systems, vol. 10, no. 5 ,pp. 566 - 581 , 2002.

- N. Weste and D. Harris, CMOS VLSI Design: A Circuits and System Perspective, 3rd ed. Reading, MA, USA: Addison-Wesley May 2004.

- H.-.M. Lam and C.-Y. Tsui, "A MUX-based high-performance single-cycle CMOS comparator," IEEE Transaction on Circuits System II, vol.54, no.7, pp.591-595, 2007.

- [4] Sharma. A, Sharma. P, "Area and power efficient 4-bit comparator design by using 1-bit full adder module," IEEE conference on Parallel, Distributed and Grid Computing, pp. 1-6, 2014.

- Subodh Wairya, Rajendra Kumar Nagaria, Sudarshan Tiwari, "Comparative performance analysis of XOR/XNOR function based high-speed CMOS full adder circuits for low voltage VLSI design," International Journal of VLSI Design & Communication System, vol.3, no.2, pp. 221-242, 2012.

Shashank Gautam received his Bachelor of Technology degree in Electronics and Communication Engineering from Uttar Pradesh Technical University, Lucknow, India in 2014. He is pursuing his Master of Technology degree in Electronics and Communication Engineering from Dr. A.P.J Abdul Kalam Technical University, Lucknow, India. His research interests include low power, reduction in chip area. He is a member of organizations like UACEE, IAENG and IACSIT etc.

Dr. Pramod Sharma is currently working as an assistant professor in the department of Electronics & Communication Engineering, Raja BALWANT SINGH Engineering Technical Campus, Bichpuri, Agra, Uttar Pradesh, India. He has 16 years of teaching as well as research experience in Electronics and Communication.