# CMOS-Compatible Plasmonic Nanocircuits for On-Chip Integration

Shiyang Zhu, G. Q. Lo, and D. L. Kwong

Abstract—Silicon photonics is merging as a unified platform for driving photonic based telecommunications and for local photonic based interconnect but it suffers from large footprint as compared with the nanoelectronics. Plasmonics is an attractive alternative for nanophotonics. In this work, two CMOS compatible plasmonic waveguide platforms are compared. One is the horizontal metal-insulator-Si-insulator-metal nanoplasmonic waveguide and the other is metal-insulator-Si hybrid plasmonic waveguide. Various passive and active photonic devices have been experimentally demonstrated based on these two plasmonic waveguide platforms.

Keywords—Plasmonics, on-chip integration, Silicon photonics.

### I. INTRODUCTION

CILICON photonics, where photonics devices are fabricated Jusing Si CMOS compatible materials and the manufacturing is based on the available microelectronics infrastructure, is merging as a unified platform for driving photonic based telecommunications and for local photonic based interconnect [1]. One critical issue for the seamless integration of electronics and photonics in a single chip is the significantly larger size of the photonic devices as compared with the electronic devices due to the fundamental diffraction limit as well as the relatively weak optical response in Si. A potential solution for this issue is to exploit the special physics of surface plasmon polariton (SPP) propagating in metal dielectric structures (namely, plasmonics) because the SPP waveguides can confine the optical mode far beyond the diffraction limit, thus enabling to reduce the dimension of optical devices to comparable to electronic devices [2]. Moreover, the incorporation of metal and dielectrics in plasmonics may provide additional potential to design novel photonic devices. However, the SPP waveguides suffer from a fundamental tradeoff between the tight mode confinement and the long propagation loss due to the inevitable metal loss. To overcome this tradeoff, on one hand, one needs to improve the propagation distance of plasmonic waveguide without sacrificing the confinement by optimization of waveguide structure and material property, and on the other hand, one needs to implement both plasmonics and conventional dielectric waveguide based photonics in the same chip so that the plasmonic waveguides will be used to realize functional

Shiyang Zhu, G. Q. Lo, and D. L. Kwong are with the Institute of Microelectronics, A\*STAR (Agency for Science, Technology and Research), Singapore 117685, Singapore (phone: 65-67705746; fax: 65-67731914; e-mail: zhusy@ime.a-star.edu.sg).

This work was supported by the Science and Engineering Research Council of A\*STAR (Agency for Science, Technology and Research), Singapore Grant 092-154-0098.

ultracompact plasmonic devices while the conventional dielectric waveguide will be used to propagate the optical signal over a long distance.

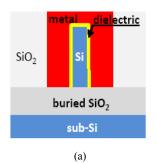

Various plasmonic waveguide structures as well as passive and active plasmonic devices based on these plasmonic waveguides have been proposed and/or demonstrated with their own advantages and disadvantages [3]. In this paper, we present two CMOS-compatible plasmonic waveguide platforms as shown schematically in Fig. 1. One is the horizontal metal-insulator-Si-insulator-metal (MISIM) nanoplasmonic waveguide [4], [5] and the other is the vertical metal-insulator-Si (MIS) hybrid plasmonic waveguide [6]. Both plasmonic waveguides are inherently a typical MOS capacitor, thus enabling to actively modulate the propagation property by an external voltage applied between the metal cover and the Si core.

Fig. 1 Two CMOS compatible plasmonic waveguide platforms for plasmonic nanocircuits: (a) horizontal metal-insulator-Si-insulator-metal (MISIM) nanoplasmonic waveguide, and (b) vertical metal-insulator-Si (MIS) hybrid plasmonic waveguide.

# II. EXPERIMENTAL

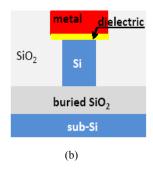

The metal used in plasmonics is usually Ag or Au because they provide a relatively low metal loss at  $1.55\mu m$  telecom wavelengths. However, both Ag and Au are not CMOS compatible. Among the CMOS-compatible metals, it has found that Cu is the best choice for  $1.55\mu m$  telecom wavelengths due to its relatively low metal loss around this wavelength [7]. Therefore, Cu is used as the metal in this work. The plasmonic devices based on the above two plasmonic waveguides can be fabricated with a similar fabrication flow, as shown schematically in Fig. 2 except that some additional steps (i.e.,  $SiO_2$  deposition and chemical mechanical polishing) are required for the MIS waveguides.

Fig. 2 Schematic fabrication flow for the MISIM plasmonic waveguide, the MIS plasmonic waveguide can be fabricated using similar flow but with additional SiO<sub>2</sub> deposition and CMP steps

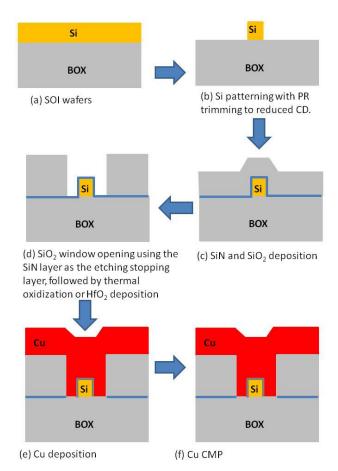

Both plasmonic waveguides are inserted in conventional Si channel waveguides with a tapered coupler, as shown schematically in Fig. 3 (a). Fig. 3 (b) shows photography of a final chip. The Cu covered area is defined the plasmonic area. The chips are be measured by conventional fiber-waveguide-fiber method as the conventional Si photonic chips.

The diced chips were measured using a fiber-to-fiber measurement setup. Quasi-TE-polarized light (for the MISIM nanoplasmonic waveguides) or Quasi-TM-polarized light (for the MIS hybrid plasmonic waveguides) is coupled into the input Si channel waveguide from a lensed polarization-maintaining (PM) single-mode fiber, transports through the waveguide, and then is coupled out to another fiber to be measured by a power meter and an optical spectrum analyzer (OSA). A semi-auto micrometer piezo-stage was used to adjust both input and output fibers to search the maximum output power.

Numerical simulation was performed using commercial software Lumerical<sup>TM</sup>. The refractive indices of  $Si_3N_4$  and  $SiO_2$  are set to 2.0 and 1.444, respectively, and the complex index of Cu at 1550 nm is set to 0.282 + j11.05.

Fig. 3 (a) Schematic layout of plasmonic waveguide (as well as plasmonic waveguide based devices) inserted in conventional Si channel waveguide. A tapered coupler can reduce the coupling loss between the plasmonic waveguide and the conventional Si waveguide, (b) photography of the final chip, the Cu-covered area is defined the plasmonic area

### III. RESULTS AND DISCUSSION

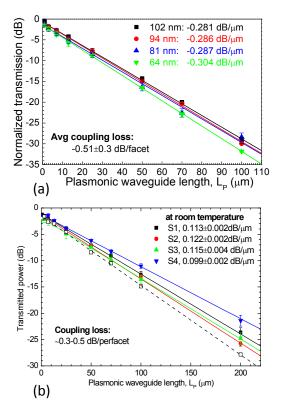

The differences between these two plasmonic waveguides are investigated both theoretically and experimentally. Because the SPP excitation requires the electric field of optical mode perpendicular to the metal/dielectric interface, the MISIM nanoplasmonic waveguides support transverse electric (TE)-polarized light while the MIS hybrid plasmonic waveguides support transverse magnetic (TM)-polarized light. Besides this obvious difference, we can see that the MISIM nanoplasmonic waveguides can confine the optical mode more tightly than the MIS hybrid plasmonic waveguides. As a result, the MISIM nanoplasmonic waveguides exhibit larger propagation loss than the MIS hybrid plasmonic waveguides. Fig. 4 shows the measured output power on straight plasmonic waveguides with different length (L<sub>P</sub>), normalized by that measured on the corresponding reference Si channel waveguide without the plasmonic area. For both kinds of plasmonic waveguides, we can see that the output power depends on L<sub>P</sub> almost linearly, from which, the propagation loss can be extracted. For example, a Cu-SiO<sub>2</sub>-Si-SiO<sub>2</sub>-Cu nanoplasmonic waveguide with ~21-nm-wide Si core and ~12-nm-thick SiO<sub>2</sub> exhibits propagation loss of ~0.63 dB/µm, and a Cu-SiO<sub>2</sub>-Si hybrid plasmonic waveguide with ~160nm×304-nm Si core and ~20-nm-thick SiO<sub>2</sub> exhibits propagation loss of ~0.12 dB/µm.

Fig. 4 Measured output power measured on straight plasmonic waveguide versus the plasmonic waveguide length, normalized by that measured on the reference Si waveguide without the plasmonic area: (a) MISIM nanoplasmonic waveguide, and (b) MIS hybrid plasmonic waveguide

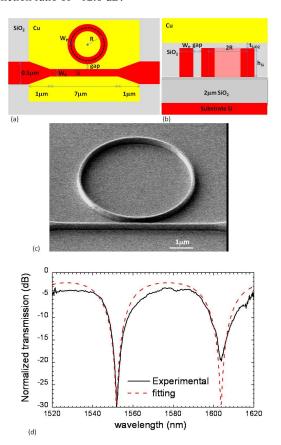

Various passive devices, including ultracompact bends, power splitters, Mach-Zehnder interferometers, waveguidering resonators, TE/TM splitters, and polarization rotators have been experimentally demonstrated based on the above two plasmonic waveguides using standard CMOS technology. In general, the MISIM plasmonic waveguides support sharp bending with lower bending loss owing to the tight optical mode confinement as compared with the MIS hybrid plasmonic waveguides, while the MIS hybrid plasmonic waveguides support evanescent coupling as the conventional dielectric waveguides, thus enabling to realize waveguide-ring resonators with relatively large quality factor. Fig. 5 shows the schematic layout of the plasmonic ring resonators. The straight bus plasmonic waveguide has length of 7µm and width (W<sub>P</sub>) of 0.18 µm, which is linked with input/output 0.5-µm-wide Si strip waveguides through 1-um-long tapered couplers. A microring adjacent to the bus waveguide has the same width of 0.18µm and the central radius (R) of 2.59µm. The separation gap between the ring and bus waveguide is 0.2 µm. Fig. 5 (c) is a SEM image of the Si core of the fabricated plasmonic ring resonator. Fig. 5 (d) is the transmission spectrum measured on the resonator, normalized by that measured on the corresponding 7-µm-long straight plasmonic

waveguide. One sees that it exhibits quality factor of  $\sim$ 275 and extinction ratio of  $\sim$ 12.8 dB.

Fig. 5 The Cu-SiO<sub>2</sub>-Si hybrid plasmonic waveguide-based WRRs: (a) Schematic layout, (b) Cross section, (c) SEM image of the patterned Si core of a typical WRR with R of 2.59μm, and (d) The measured transmission spectrum, normalized by that measured on corresponding 7-μm-long straight plasmonic waveguide

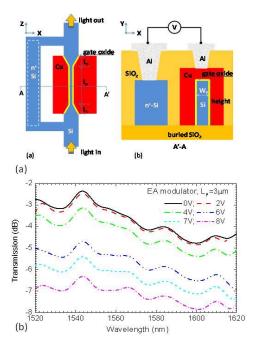

The plasmonic modulators have also been demonstrated based on these two plasmonic waveguides, which rely on the voltage induced electron accumulation at the dielectric/Si interface. With the concentration of accumulated electrons increasing, the real part of Si refractive index decreases and the imaginary part increases. The real part of Si refractive index can be close or even smaller than the dielectric refractive index if the electron concentration in the accumulation layer is high enough (e.g., ~6×10<sup>20</sup>cm<sup>-3</sup>), thus the optical mode will be mostly confined in this narrow (~1 nm) accumulation layer, which in turn modulate the effective modal index (both the real and imaginary parts) of the plasmonic waveguides, as shown in Fig. 6. Electro-absorption and phase modulators with ultracompact size (e.g., ~3µm long) have been experimentally demonstrated, as shown in Fig. 7.

Fig. 6 (a) Spatial electron distribution in a Cu/5-nm-SiO<sub>2</sub>/n-Si capacitor, as shown schematically in inset, under different voltages, obtained from 1-D MEDICI simulation; and (b) Real part (n) and imaginary part (k) of Si complex index as a function of free electron concentration based on the Drude model

Fig. 7 (a) Schematic of a proof-of-concept Si plasmonic modulator based on the horizontal MISIM plasmonic waveguide: (a) top view and (b) cross-sectional view along A-A', and (b) Transmission spectra measured on an EA modulator with 3-μm L<sub>P</sub> under voltage ranging from 0 to 8V, normalized by the spectrum measured on a reference Si waveguide without the plasmonic structure

### IV. CONCLUSION

Two CMOS-compatible plasmonic waveguide platforms are developed as horizontal Cu-insulator-Si-insulator-Cu nanoplasmonic waveguide and vertical Cu-insulator-Si hybrid plasmonic waveguide. Various passive and active plasmonic devices are demonstrated based on these two platforms using standard CMOS technology. Although the performance of the demonstrated ultra-compact plasmonic modulators is not good at this stage, it can be significantly improved as predicted theoretically (i.e., up to 100 GHz, which is difficult for conventional Si modulators).

## REFERENCES

- D. J. Lockwood and L. Pavesi, "Silicon photonics II: components and integration", Topic in Applied Physics, vol. 119, Springer-Verlag, Berlin (2011)

- E. Ozbay, "Plasmonics: merging photonics and electronics at nanoscale

- dimensions," Science, vol. 311, pp. 189-193 (2006). S. I. Bozhevolnyi, "Plasmonic: nanguides and circuits," Pan Stanford Pulishing Pte. Ltd. (2009).

- S. Y. Zhu, T. Y. Liow, G. Q. Lo, and D. L. Kwong, "Fully complementary metal-oxide-semiconductor compatible nanoplasmonic slot waveguides for silicon electronic photonic integrated circuits,' Appl. Phys. Lett., vol. 98, art no. 021107 (2011).

- Y. Zhu, T. Y. Liow, G. Q. Lo, and D. L. Kwong, "Silicon-based horizontal nanoplasmonic slot waveguides for on-chip integration,' Optics Express, vol. 19, pp. 8888-8902 (2011).

- S. Y. Zhu, G. Q. Lo, and D. L. Kwong, "Experimental demonstration of vertical Cu-SiO2-Si hybrid plasmonic waveguide components on an SOI platform," IEEE Photo. Tech. Lett., vol. 24, pp. 1224-1226 (2012).

- S. Y. Zhu, G. Q. Lo, and D. L. Kwong, "Components for silicon plasmonic nanocircuits based on horizontal Cu-SiO<sub>2</sub>-Si-SiO<sub>2</sub>-Cu nanoplasmonic waveguides," Optics Express, vol. 20, pp.5867-5881,  $(201\hat{2}).$