# Inversion Layer Effective Mobility Model for Pocket Implanted Nano Scale n-MOSFET

Muhibul Haque Bhuyan, Member, IEEE, and Quazi D. M. Khosru, Member, IEEE

Abstract—Carriers scattering in the inversion channel of n-MOSFET dominates the drain current. This paper presents an effective electron mobility model for the pocket implanted nano scale n-MOSFET. The model is developed by using two linear pocket profiles at the source and drain edges. The channel is divided into three regions at source, drain and central part of the channel region. The total number of inversion layer charges is found for these three regions by numerical integration from source to drain ends and the number of depletion layer charges is found by using the effective doping concentration including pocket doping effects. These two charges are then used to find the effective normal electric field, which is used to find the effective mobility model incorporating the three scattering mechanisms, such as, Coulomb, phonon and surface roughness scatterings as well as the ballistic phenomena for the pocket implanted nano-scale n-MOSFET. The simulation results show that the derived mobility model produces the same results as found in the literatures.

Keywords—Linear Pocket Profile, Pocket Implanted n-MOSFET, Effective Electric Field and Effective Mobility Model.

#### I. INTRODUCTION

S the channel length of MOSFETs is scaled down to A deep-submicrometer or nano scale regime, we observe the reduction of threshold voltage with the reduction of channel length [1]. This effect is known as short-channel effect (SCE). It can be reduced or can be even reversed (then it is called reverse short channel effect or RSCE) by locally raising the channel doping near source and drain junctions. RSCE was originally observed in MOSFETs due to oxidation-enhanced-diffusion [2] or implant-damage-enhanced diffusion [3]. Lateral channel engineering utilizing halo or pocket implant [4]-[8] surrounding drain and source regions is effective in retarding SCE with the downscaling of the channel length of the MOS devices. In fact, this pocket implant technology is found to be very promising in the effort to tailor the short-channel performances of deep-submicron as well as nano scale MOSFETs [5]. It could be shown that with an optimized pocket implant process the saturation current is up to 10% higher compared to a conventional optimized junction technology without increasing the leakage current of the devices minimum channel length [9]. The inversion layer mobility in Si MOSFET's has been a very important physical

Muhibul Haque Bhuyan is a Ph.D. candidate in the Department of Electrical and Electronic Engineering (EEE) of Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh and he is with the Department of Electrical and Computer Engineering, Presidency University, Dhaka, Bangladesh. e-mail: (muhibulhb@gmail.com).

Quazi Deen Mohd Khosru is with the Department of Electrical and Electronic Engineering (EEE) of Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh. e-mail: (qdmkhosru@eee.buet.ac.bd).

Manuscript received December 17, 2010; revised January 14, 2011.

quantity as a parameter to describe the drain current and a probe to study the electric properties of a two-dimensional carrier system. Therefore, much study [10] since the 1960's has revealed dominant scattering mechanisms determining the mobility. On the other hand, it has already been reported that the electron and hole mobilities in the inversion layer on a (100) surface follow the universal curves at room temperature independent of the substrate impurity concentration or the substrate bias when plotted as a function of effective normal fields,  $\mathcal{E}_{eff}$  [11]. Since the use of pocket implants causes a strong non-uniform lateral doping profile and with the reduction of channel length or with the increase of pocket profile parameters there is a pronounced increase of the effective channel doping concentration, the effective mobility is supposed to be degraded further due to Coulomb scattering with the ionized dopants and charged interface traps at low vertical electric fields i.e. at low gate bias voltage. This is called roll-off region. As the effective vertical field increases, the mobility becomes independent of the channel doping and all the samples approach the so-called universal curve. In this region, the main scattering processes are phonon and surface roughness scattering that do not depend on channel doping. In most circuit models [12]-[14], simple mobility models [15], [16] are used to describe the effective surface mobility neither accounting for the degradation by Coulomb scattering in heavily doped MOSFET's (only the so called 'universal curve' [17] is modeled) nor accounting for the lateral non-uniform doping profile. This neglect can cause simulation errors in the transconductance of short n-MOS pocket implanted devices of up to 50% which can not be tolerated in today's circuit simulations [9]. In this paper, an analytical inversion layer effective mobility model is developed taking into account the pocket doping as well as temperature effects for the nano scale pocket implanted n-MOSFET. The model is developed using two linear pocket doping profiles at the surface of the device. The total number of inversion layer and depletion charges is calculated numerically using the threshold voltage and the surface potential models of pocket implanted n-MOSFET published in [18] and [19] respectively. Then these two charges are used to find the effective normal electric field, which is used to obtain effective mobility model incorporating the Coulomb, phonon and surface roughness scatterings as well as the ballistic phenomena. The pocket profile parameters and device parameters as well as bias voltages are varied to investigate the pocket implantation effect on effective mobility. As a verification of the mobility model, a subthreshold drain current model in [20] is simulated incorporating this mobility

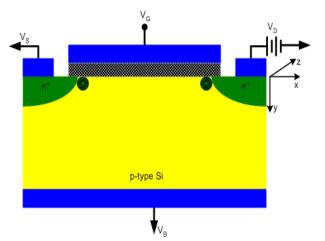

Fig. 1. Pocket implanted n-MOSFET structure

#### II. POCKET DOPING PROFILE

The pocket implanted n-MOSFET structure shown in Fig. 1 is considered in this work and assumed co-ordinate system is shown at the right side of the structure. Localized extra dopings are shown by circles near the source and drain side regions. All the device dimensions are measured from the oxide-silicon interface. In the structure, the junction depth  $(r_j)$  is 25 nm. The oxide thickness  $(t_{ox})$  is 2.5 nm, and it is SiO<sub>2</sub> with fixed oxide charge density of  $10^{11}$  cm<sup>-2</sup>. Uniformly doped p-type Si substrate is used with doping concentration  $(N_{sub})$  of  $4.2\times10^{17}$  cm<sup>-3</sup> with pocket implantation both at the source and drain side with peak pocket doping concentration of  $1.75\times10^{18}$  cm<sup>-3</sup> and pocket lengths from 20 to 30 nm, and source or drain doping concentration of  $9.0\times10^{20}$  cm<sup>-3</sup>.

The pocket implantation, which causes the Reverse Short Channel Effect (RSCE), is done by adding impurity atoms both from the source and drain edges. It is assumed that the peak pocket doping concentration  $(N_{pm})$  gradually decreases linearly towards the substrate level concentration  $(N_{sub})$  with a pocket length  $(L_p)$  from both the source and drain edges. The basis of the model of the pocket is to assume two laterally linear doping profiles from both the source and drain

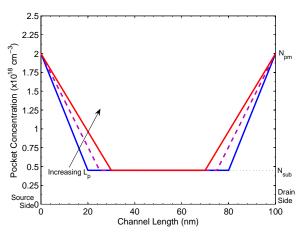

Fig. 2. Simulated pocket profiles at the surface for different pocket lengths,  $L_p = 20$ , 25 and 30 nm; peak pocket concentration,  $N_{pm} = 2.0 \times 10^{18}$  cm<sup>-3</sup>

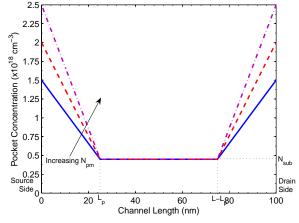

edges across the channel as shown in Figs. 2-3 for substrate concentration of  $4.2\times10^{17}~{\rm cm^{-3}}$  and channel length of 100 nm. The pocket parameters,  $N_{pm}$  and  $L_p$ , play important role in determining the RSCE. At the source side, the pocket profile is given as

$$N_s(x) = -\frac{N_{pm} - N_{sub}}{L_p} x + N_{pm}$$

$$N_s(x) = N_{sub} \frac{x}{L_p} + N_{pm} \left( 1 - \frac{1}{L_p} x \right)$$

(1)

At the drain side, the pocket profile is given as

$$N_d(x) = \frac{N_{pm} - N_{sub}}{L_p} [x - (L - L_p)] + N_{sub}$$

$$N_d(x) = N_{sub} \left( \frac{L}{L_p} - \frac{1}{L_p} \right) + N_{pm} \left( 1 - \frac{L}{L_p} + \frac{1}{L_p} x \right)$$

(2)

,where x represents the distance across the channel. Since these pile-up profiles are due to the direct pocket implantation at the source and drain sides, the pocket profiles are assumed symmetric at both sides.

$$N_{eff} = \frac{1}{L} \int_{0}^{L} \left[ N_{s}(x) + N_{d}(x) + N_{sub} \right] dx$$

(3)

With these two conceptual pocket profiles of equations (1) and (2), the profiles are integrated mathematically along the channel length from the source side to the drain side and then the integration result is divided by the channel length (L) to derive an average effective doping concentration  $(N_{eff})$  as shown in equation (3).

$$N_{eff} = N_{sub} \left( 1 - \frac{L_p}{L} \right) + \frac{N_{pm} L_p}{L} \tag{4}$$

Putting the expressions of  $N_s(x)$  and  $N_d(x)$  from equations (1) and (2) in equation (3) the effective doping concentration is obtained in equation (4). This effective doping concentration expression is then used in deriving the surface potential model

Fig. 3. Simulated pocket profiles at the surface for various peak pocket concentrations,  $N_{pm}=1.5\times10^{18},\ 2.0\times10^{18},\ 2.5\times10^{18}\ {\rm cm^{-3}};$  pocket length,  $L_p=25\ {\rm nm}$

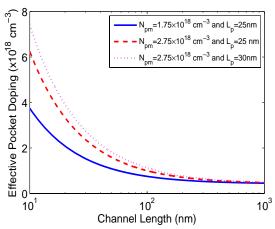

Fig. 4. Simulated effective pocket doping concentration vs. channel lengths at the surface for different peak pocket concentration and pocket lengths with substrate concentration,  $N_{sub}=4.5\times10^{17}~{\rm cm}^{-3}$

by applying Gauss's law [19]. This surface potential model is used to find the inversion layer charges and other parameters for determining the effective inversion layer mobility. When  $L_p \ll L$  for long channel device then the pocket profile has very little effect on uniform substrate concentration at the surface, but when  $L_p$  is comparable with L then the pocket profile parameters affects the substrate doping concentration at the surface of the n-MOSFET. This causes the surface potential, threshold voltage and hence effective mobility to change due to RSCE.

Because of the pocket implantation, effective doping concentration increases with decreasing channel lengths as observed in Fig. 4. This becomes stronger when both peak pocket concentration and/or pocket length increases.

# III. MODELING OF THE INVERSION LAYER EFFECTIVE MOBILITY

According to the universal mobility model [16], the effective normal electric field,  $\mathcal{E}_{eff}$  is defined by equation (5).

$$\mathscr{E}_{eff} = \frac{1}{\varepsilon_{Si}} \left( Q_{dep} + \eta Q_{inv} \right) \tag{5}$$

,where  $\varepsilon_{Si}$  is the permittivity of Si,  $Q_{dep}$  is the surface depletion charge per unit area,  $Q_{inv}$  is the surface inversion carrier charge per unit area. Here,  $\eta$  is a key parameter in defining the shape of the effective normal electric field,  $\mathscr{E}_{eff}$  defined by the equation (5). In order to provide the universal relationship (i.e. the substrate bias and substrate concentration independence of effective mobility vs. effective normal electric field curve), the value of  $\eta$  should taken to be 1/2 for the electron mobility [16] and 1/3 for the hole mobility [21]. This relationship has been often utilized as a precise mobility model in device simulators [22], [23].

$$\mathscr{E}_{eff} = \frac{C_{ox}}{\varepsilon_{Si}} \left[ \eta(V_{gs} - V_{th}) + V_{th} - V_{FB} - 2\psi_{s,inv} \right]$$

(6)

The depletion charge in equation (5) can be determined by the threshold voltage equation [18] and the inversion layer change can be determined from  $Q_{inv} = C_{ox}(V_{gs} - V_{th})$ . Thus equation (5) can be transformed in to equation (6), where  $V_{GS}$  is the gate voltage and  $V_{th}$  is the threshold voltage of the pocket implanted n-MOSFET [18],  $V_{FB}$  is the flat band voltage and  $C_{ox}$  is the oxide capacitance per unit area. There has been much study on effective mobility [10] since the 1960's. This has revealed that the dominant scattering mechanisms determine the mobility. The three most relevant scattering processes in MOSFET devices are the (screened) Coulomb scattering, the phonon scattering and the surface roughness scattering through which the electrons exchange momentum and kinetic energy with their environment. All these tend to lower the mobility of electrons in the inversion layer to values smaller than the bulk mobility. Based on these scattering processes three mobility models are derived for the pocket implanted MOSFET. Each of these three terms has been modeled analytically as functions of the variables  $N_{eff}$  (effective channel dopant density for the pocket implantation case),  $N_{inv}$  (inversion layer electron density) and T (temperature).

#### A. Coulomb scattering mobility model

A formula for the Coulomb limited mobility model is given by S. Villa et al [17]. This is modified for our pocket implanted n-MOSFET incorporating our effective pocket doping concentration from equation (4) and is given in equation (7).

$$\mu_{cb} = \mu_0 \frac{L_s}{N_{eff} L_{th} L_{DH}} \left( 1 + \frac{L_{th}}{L_s} \right)^2 \tag{7}$$

,where  $L_s=\sqrt{L_{DH}^2+L_{TF}^2}$  is the effective screening length that has the dependence on the carrier density with  $L_{TF}=\frac{(\pi\hbar^2\varepsilon_{Si})}{(q^2m_{n,eff})}$  being the Thomas-Fermi value in the fully degenerate case where q is the electronic charge,  $m_{n,eff}$  is the effective mass for electron,  $L_{th}=\hbar/\sqrt{2kTm_{n,eff}}$  is the thermal length of the carriers where k is the Boltzmann constant and T being the temperature and  $L_{DH}=\frac{(2kT\varepsilon_{Si})}{(qQ_{inv})}$  is the Debye-Huckle value.

# B. Phonon scattering mobility model

Gamiz et al. [24] have shown that the phonon limited mobility may be approximated by equation (8) taking the temperature influence into account. We just modified this equation with our effective field expressions since this equation was derived from a detailed Monte Carlo analysis of phonon scattering in quantized inversion layers and thus it may be regarded as the one reproducing the most recent theoretical results

$$\mu_{ph} = \mu_{phB} \left[ \left( \frac{T}{T_0} \right)^n + \left( \frac{T}{T_0} \right)^r \left( \frac{\mathscr{E}_{eff}}{\mathscr{E}_0} \right)^{\alpha(T)} \right]^{-1} \tag{8}$$

,where  $\mu_{phB}(300K)=1470~{\rm cm^2/V}$ -sec is the phonon limited bulk mobility,  $n=2.109,~r=1.7,~\mathcal{E}_0=7\times 10^4$  V/cm and  $\alpha(T)=0.2(T/T_0)^{-0.1}$  with  $T_0$  is another fitting parameter or base temperature taken as 300 K.

#### C. Surface roughness scattering mobility model

The Si-SiO<sub>2</sub> interface is not ideally flat, but shows irregularities with a typical amplitude of one or two atomic layers. Scattering by this potential fluctuations degrades the carrier mobility at high effective fields. A detailed TEM analysis of the interface between Si and a thermally grown oxide was performed by Goodnick and coworkers [25] and their results have been taken as a reference in many following theoretical and numerical works. In their study, the roughness of the Si-SiO<sub>2</sub> interface appeared to be characterized by an r.m.s. displacement of about 0.2 nm and a correlation length of about 1.3 nm, that is, about half the electron thermal length at room temperature. This means that on the spatial scale of the carrier wavelength, the surface potential appears almost uncorrelated, thus featuring an almost constant power spectrum.

$$\mu_{sr} = \delta \mathcal{E}_{eff}^{-2} \tag{9}$$

As long as this condition holds, the surface roughness mobility is inversely proportional to the square of the effective electric field as given in equation (9) [26], [27]. But this formula neglects the effects of carrier scattering, which is responsible for a weak temperature dependence of this term. In fact, as the temperature increases, the screening of the scattering potential weakens and the mobility decreases. We have accounted for the effect by modifying the term,  $\delta$  according to the equation (10).

$$\mu_{sr} = \delta e^{-\left(\frac{T}{T_0}\right)^2} \mathcal{E}_{eff}^{-\gamma} \tag{10}$$

,where  $\delta$  and  $\gamma$  are fitting parameters depending on the quality of the Si-SiO<sub>2</sub> interface. However, in this work, we have used  $\delta = 8.8 \times 10^{14}$  V/sec and  $\gamma = 2$ .

The equivalent mobility ( $\mu_{eqv}$ ) is the total mobility that considers the effects of all scattering mechanisms. These are combined with the Mathiessen's rule [1] as in equation (11).

$$\frac{1}{\mu_{eqv}} = \frac{1}{\mu_{cb}} + \frac{1}{\mu_{ph}} + \frac{1}{\mu_{sr}} \tag{11}$$

The curve of equivalent mobility versus effective normal electric field follows the universal relationship [11], [28].

#### D. Ballistic mobility model

The effective electron mobility in short channel (nano scaled) MOSFETs must be much smaller than the electron mobility in long channel devices. This reduction was predicted for ballistic devices in [29]-[31]. Equivalent mobility ( $\mu_{eqv}$ ) determined in this way is not applicable for nano scale MOSFET. If the nano scale device physics is not considered in the mobility curve, the mobility is termed as the ballistic or apparent mobility [32]. The physical reasons for a drastic mobility reduction are related to the ballistic motion first predicted in 1979 [33], [34]. In ballistic field effect transistors, electrons travel from the source to the drain ideally without any collisions with impurities or phonons. Electrons propagate in the device channel with a randomly oriented thermal velocity,  $v_{th}$ , (or with a Fermi velocity,  $v_F$ , for a degenerate electron

gas) and, hence, have only a limited time to accelerate in the electric field and acquire a drift velocity. Their transit time is determined by  $L/v_{th}$ , where L is the device length, (or by  $L/v_F$  in a degenerate case). As a result, in low electric fields, the current is proportional to the electric field and to the electron concentration, just like in the collision-dominated case. Therefore, for MOSFETs with nano scale channel lengths, the mobility thus obtained has to be modified. It has been observed that the mobility extracted from electrical characteristics decreases with the shrinking of the channel length (L). The equivalent mobility determined by equation (11) is said to be apparent mobility. The electron mobility has to be substituted by a parameter that we call ballistic mobility [29], [30], [35] which (for a non-degenerate electron gas) is given by equation (12) [30].

$$\mu_{bal} = \frac{2qL}{\pi m_{n,eff} v_{th}} \tag{12}$$

,where  $v_{th}$  is the average thermal velocity of the electron in the channel and is given by equation (13) [32].

$$v_{th} = \sqrt{\frac{8kT}{\pi m_{n,eff}}} \tag{13}$$

The equivalent mobility may be linked to the ballistic mobility using Matthiessen's rule and thus equivalent electron mobility can be determined by equation (14).

$$\frac{1}{\mu_{eff}} = \frac{1}{\mu_{eqv}} + \frac{1}{\mu_{bal}} \tag{14}$$

It should be noted that Matthiessen's rule tacitly assumes the momentum relaxation time due to the different scattering mechanisms have the same energy dependence. In order to correctly account for the various scattering sources a weighted statistical averaging of the relaxation times should be performed. Nevertheless Matthiessen's rule should give a good first-order approximation, especially when valley reproduction is taken in to account [36].

#### IV. RESULTS AND DISCUSSIONS

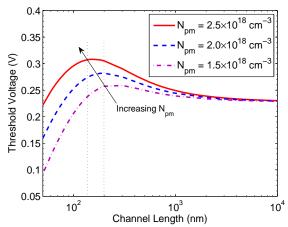

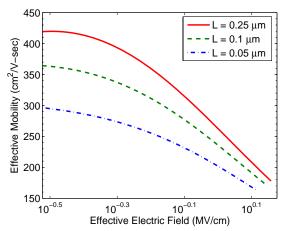

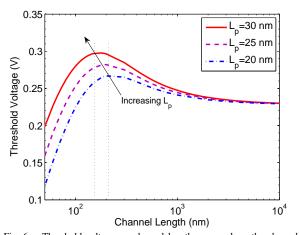

Figs. 5-6 show threshold voltage variation with gate lengths for different pocket doses and pocket lengths respectively. It has been observed that as the pocket dose or the pocket length is increased the reverse short channel effect increases and thus delays the threshold voltage roll off. Since mobility is affected by the threshold voltage, therefore, variation of pocket dose or pocket length will cause the variation of the effective mobility. From the  $\mathscr{E}_{eff}$  dependence curves of the different types of mobility models as shown in Fig. 3 of [11], it is observed that the phonon scattering and surface roughness scattering mechanisms dominate at the higher value of electric field since the carrier concentration is higher and the mobility due to Coulomb scattering dominates at low value of effective normal electric field due to the low value of inversion charge. Fig. 7 shows the variation of the effective mobility with the variation of effective electric field for the different channel lengths. It is observed that as the channel length decreases the effective mobility decreases because scattering increases in the

Fig. 5. Threshold voltage vs. channel length curves along the channel for various peak pocket doping concentration with  $V_{BS}=0.0~{\rm V},\,V_{DS}=0.0~{\rm V}$  and pocket length,  $L_p=25~{\rm nm}$

Fig. 7. Effective mobility vs. effective electric field for different channel lengths (L) with  $N_{sub}=3.5\times10^{17}~{\rm cm^{-3}},~N_{pm}=1.75\times10^{18}~{\rm cm^{-3}},~L_p=25~{\rm nm},~V_{DS}=0.05~{\rm V},~T=300~{\rm K}$

Fig. 6. Threshold voltage vs. channel length curves along the channel for various peak pocket doping concentration with  $V_{BS}=0.0$  V,  $V_{DS}=0.0$  V and and peak pocket doping concentration,  $N_{pm}=1.75\times10^{18}$  cm $^{-3}$

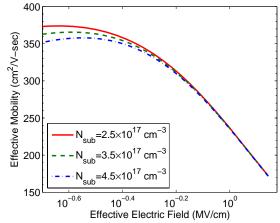

Fig. 8. Effective mobility vs. effective electric field for different substrate concentrations  $(N_{sub})$  with  $L=0.1~\mu\text{m},~N_{pm}=1.75\times10^{18}~\text{cm}^{-3},~L_p=25~\text{nm},~V_{DS}=0.05~\text{V},~T=300~\text{K}$

device with lower channel length. But at lower values of the electric fields mobility tends to degrade. This can be ascribed to coulomb scattering term at the lower values of effective normal electric fields. Fig. 8 shows that the effective mobility is not changed much with the variation of the substrate doping concentration. But at very low electric fields the effective mobility degrades with the increase of the substrate doping concentration, because then the Coulomb scattering rate dominates over the surface roughness and phonon scattering rate as observed in Fig. 3 of [11]. Because at higher substrate doping more ionized ions are available at the surface.

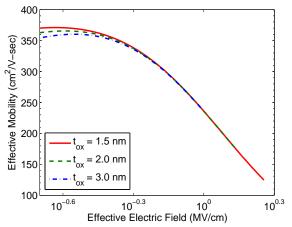

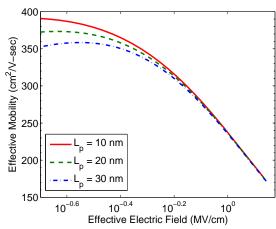

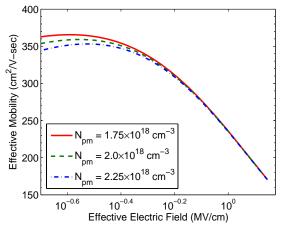

Fig. 9 shows the variation of the effective mobility with the variation of effective electric field for the different oxide thicknesses. It is observed that as the oxide thickness decreases the effective mobility increases at lower electric fields because now the gate has more control over the channel. This can be ascribed to coulomb scattering term at the lower values of effective normal electric fields. But mobility does not change appreciably when the electric field is very high. For Figs. 10-

11, the same explanation may be given. That is, increased pocket dose and pocked length cause the effective mobility to degrade at low values of normal electric fields because of the increased Coulomb scattering rate due to the incorporation of the more ions in the channel by the pocket implantation. But at the higher value of the effective normal electric field, there is no deviation in the effective mobility curve due to the change of pocket profile parameters. This holds the universality of the effective mobility curve.

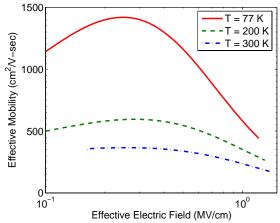

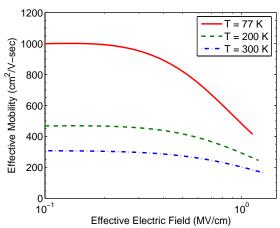

Figs. 12-13 show the variation of effective mobility with the effective electric field for different temperatures and two different channel lengths of 100 nm and 50 nm. It is observed that as the temperature goes down the effective mobility increases because with the decrease of temperature, carriers scattering is less at the surface. But when the electric field is low then the mobility goes down for a particular temperature because of the increase of the coulomb scattering. Due to pocket implantation, threshold voltage has not decreased until 100 nm, but at 50 nm channel length threshold voltage has

Fig. 9. Effective mobility vs. effective electric field for different oxide thicknesses  $(t_{ox})$  with  $N_{sub}=3.5\times10^{17}$  cm $^{-3}$ ,  $N_{pm}=1.75\times10^{18}$  cm $^{-3}$ ,  $L_p=25$  nm,  $V_{DS}=0.05$  V, T=300 K

Fig. 11. Effective mobility vs. effective electric field for different pocket lengths ( $L_p$ ) with  $L=0.1~\mu\mathrm{m},~N_{sub}=3.5\times10^{17}~\mathrm{cm}^{-3},~L_p=25~\mathrm{nm},~N_{pm}=1.75\times10^{18}~\mathrm{cm}^{-3},~V_{DS}=0.05~\mathrm{V},~T=300~\mathrm{K}$

Fig. 10. Effective mobility vs. effective electric field for different peak pocket doping concentrations  $(N_{pm})$  with  $L=0.1~\mu\mathrm{m},\,N_{sub}=3.5\times10^{17}~\mathrm{cm}^{-3},\,L_p=25~\mathrm{nm},\,V_{DS}=0.05~\mathrm{V},\,T$  = 300 K

Fig. 12. Effective mobility vs. effective electric field for different temperatures (T) with  $L=0.1~\mu\text{m},~N_{sub}=4.5\times10^{17}~\text{cm}^{-3},~L_p=25~\text{nm},~N_{pm}=1.75\times10^{18}~\text{cm}^{-3},~V_{DS}=0.05~\text{V}$

already decreased due to SCE as shown in Figs. 5-6. Hence at very low values of the effective normal electric field, the mobility curve becomes flat at lower temperature for the shorter channel length device.

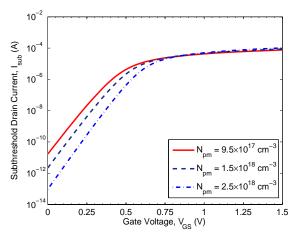

In order for the further verification of the proposed model, subthreshold drain current model is simulated incorporating the proposed effective mobility model. The model is simulated for three different pocket doses as shown in Fig. 14. It is observed that the subthreshold drain current behavior with the gate voltage variation is same as observed in [20]. As the pocket dose is increased the subthreshold drain current is decreased for a particular gate bias due to the increase of the pocket dose and hence the increase of the Coulomb scattering rate and consequent mobility degradation.

### V. CONCLUSION

This paper has proposed an inversion layer effective mobility model for ultra thin oxide and nano scale pocket implanted n-MOSFET based on the linear pocket profiles at the source

and drain sides of the pocket implanted n-MOSFET along the channel region. The effective normal electric field has been derived from the bulk charge and the inversion layer charge. The effects of changing the pocket profiles parameters as well as device parameters on the effective mobility of the pocket implanted n-MOSFET have been studied using the proposed model. Then the subthreshold drain current has been simulated incorporating the proposed mobility model. The simulated results show that the proposed model predicts the effective mobility and the subthreshold drain current accurately for the pocket implanted n-MOSFET having channel lengths in the nano scale regime.

## ACKNOWLEDGMENT

The authors would like to acknowledge the financial support provided by the Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET) for conducting the research work.

Effective mobility vs. effective electric field for different temper-Fig. 13. atures (T) with L = 50 nm,  $N_{sub} = 4.5 \times 10^{17}$  cm<sup>-3</sup>,  $L_p = 25$  nm,  $N_{pm} = 1.75 \times 10^{18} \text{ cm}^{-3}, V_{DS} = 0.05 \text{ V}$

Fig. 14. Subthreshold drain current versus gate voltage for for different peak pocket implant concentrations with drain bias,  $V_{DS}=0.05$  V, substrate concentration,  $N_{sub}=4.5\times10^{17}~{\rm cm^{-3}}$ , pocket length,  $L_p=25~{\rm nm}$  and channel length, L = 100 nm

# REFERENCES

- [1] S. M. Sze, "Physics of Semiconductor Devices," 2nd Edition, John Wiley and Sons, New York, ch. 8, 1981.

- M. Orlowski, C. Mazure and F. Lau, "Submicron short channel effects due to gate reoxidation induced lateral interstitial diffusion," IEEE IEDM Tech. Digest, p. 632, 1987.

- [3] M. Nishida and H. Onodera, "An anomalous increase of threshold voltage with shortening the channel lengths for deeply boron-implanted n-channel MOSFETs," IEEE Trans. on Electron Devices, vol. 48, pp. 1101, 1981.

- K. Y. Lim and X. Zhou, "Modeling of Threshold Voltage with Nonuniform Substrate Doping," in Proc. of the IEEE International Conference on Semiconductor Electronics (ICSE 1998), Malaysia, pp. 27-31, 1998.

- B. Yu, C. H. Wann, E. D. Nowak, K. Noda and C. Hu, "Short Channel Effect improved by lateral channel engineering in deep-submicrometer MOSFETs," IEEE Transactions on Electron Devices, vol. 44, pp. 627-633, April 1997.

- [6] B. Yu, H. Wang, O. Millic, Q. Xiang, W. Wang, J. X. An and M. R. Lin, "50 nm gate length CMOS transistor with super-halo: Design, process and reliability," IEDM Technical Digest, pp. 653-656, 1999.

- K. M. Cao, W. Liu, X. Jin, K. Vasant, K. Green, J. Krick, T. Vrotsos and C. Hu, "Modeling of pocket implanted MOSFETs for anomalous analog behavior," IEEE IEDM Technical Digest, pp. 171-174, 1999.

- [8] Y. S. Pang and J. R. Brews, "Models for subthreshold and above subthreshold currents in 0.1  $\mu m$  pocket n-MOSFETs for low voltage applications," IEEE Transactions on Electron Devices, vol. 49, pp. 832-839, May 2002.

- [9] P. Klein and S. Chladek, "A New Mobility Model for Pocket Implanted Quarter Micron n-MOSFETs and Below," IEEE IEDM Technical Digest, pp. 1587-1590, 2001.

- [10] T. Ando, A. B. Fowler and F. Stern, "Electronic properties of two-

- dimensional systems," Rev. Mod. Phys., vol. 54, no. 2, pp. 437-472, 1982. [11] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the University of Inversion Layer Mobility in Si MOSFET's: Part I-Effects of Surface Impurity Concentration," IEEE Transactions on Electron Devices, vol. 41, pp. 2357-2362, 1994.

- [12] B. Lemaitre, "An improved analytical LDD-MOSFET model for digital and analog circuit simulation for all channel length down to deep-submicron," IEEE IEDM Technical Digest, 1991.

- [13] R. M. D. A. Velghe, D. B. M. Klaassen and F. M. Klaassen, "Compact MOS modeling for analog circuit simulation," IEEE IEDM Technical Digest, pp. 485-488, 1993.

- [14] Y. Cheng et. al., BSIM3v3 Manual, University of California, 1996.

[15] Y. P. Tsividis, "Operation and Modeling of the MOS Transistor," New York, McGraw-Hill, 1999.

- [16] A. G. Sabnis and J. T. Clemens, "Characterization of the electron mobility in the inverted <100> Si," IEEE IEDM Technical Digest, 1979, pp. 18-21.

- [17] S. Villa, A. L. Lacaita, L. M. Perron and R. Bez, "A Physically-Based Model of the Effective Mobility in Heavily-Doped n-MOSFETs,' Transactions on Electron Devices, vol. 45, no. 1, pp. 110-115, 1998.

- [18] M. H. Bhuyan and Q. D. M. Khosru, "Linear pocket profile based threshold voltage model for sub-100 nm n-MOSFET incorporating substrate and drain bias effects," in Proc. of the 5th International Conference on Electrical and Computer Engineering (ICECE 2008), Dhaka, December 20-22, 2008, pp. 447-451.

- [19] M. H. Bhuyan and Q. D. M. Khosru, "Linear profile based analytical surface potential model for pocket implanted sub-100 nm n-MOSFET, Journal of Electron Devices, ISSN 1682-3427, vol. 7, pp 235-240, April 2010.

- [20] M. H. Bhuyan and Q. D. M. Khosru, "An analytical subthreshold drain current model for pocket implanted nano scale n-MOSFET," Journal of

- Electron Devices, ISSN 1682-3427, vol. 8, pp 263-267, October 2010. [21] S. C. Sun and J. D. Plummer, "Electron mobility in inversion and accumulation layers on thermally oxidized silicon surfaces," IEEE Transactions on Electron Devices, vol. 27, pp. 1497-1508, August 1980.

- [22] S. W. Lee, "Universality of mobility-gate field characteristics of elec-trons in the inversion charge layer and its application in MOSFET modeling," IEEE Transactions on Computer-Aided Design, vol. 8, no. 7, pp. 724-730, 1989.

- [23] H. Shin, G. M. Yeric, A. F. Tasch, and C. M. Maziar, "Physically-based models for effective mobility and local-field mobility of electrons in MOS inversion layers," Solid-State Electronics, vol. 34, no. 6, pp. 545-552,

- [24] F. Gamiz, J. Lopez-Villanueva, J. Banqueri, J. Carceller and P. Cartujo, "A comparison of models for phonon scattering in silicon inversion layers," Journal of Applied Physics, vol. 77, pp. 4128-4130, 1995.

- [25] S. M. Goodnick, D. K. Ferry, C. W. Wilmsen, Z. Liliental, D. Fathy and O. L. Krivanek, "Surface roughness at the Si(100)-SiO2 interface," Phys. Rev. B, vol. 32, pp. 8171-8196, 1985.

- [26] N. D. Arora and G. SH. Gindenblat, "A semi-empirical model of the MOSFET inversion layer mobility for low-temperature operation," IEEE Transactions on Electron Devices, vol. 34, no. 1, pp. 89-93, 1987.

- [27] C. Lombardi, S. Manzini, A. Saporito and M. Vanzi, "A physicallybased mobility model for numerical simulation of non planar devices. IEEE Transactions on Computer-Aided Design, vol. 7, no. 11, pp. 1164-1170, 1988,

- [28] S. Takagi, A. Toriumi, M. Iwase and H. Tango, "On the University of Inversion Layer Mobility in Si MOSFET's: Part II-Effects of Surface Orientation," IEEE Transactions on Electron Devices, vol. 41, pp. 2363-2368, 1994.

- [29] A. A. Kastalsky and M. S. Shur, "Conductance of small semiconductor devices," Solid-State Commun., vol. 39, no. 6, p. 715, 1981.

- [30] K. Lee and M. S. Shur, "Impedance of thin semiconductor films," J. Appl. Phys., vol. 54, no. 7, pp. 4028-4034, July 1983.

[31] M. Dyakonov and M. S. Shur, "Ballistic transport in high mobility

- semiconductor," in The Physics of Semiconductors, M. Scheffler and R. Zimmermann, Eds. Singapore: World Scientific, pp. 145-148, 1996.

- [32] M. S. Shur, "Low ballistic mobility in submicron HEMTs," IEEE Electron Device Letters., vol. 23, pp. 511-513, 2002.

- [33] M. S. Shur and L. F. Eastman, "Near ballistic transport in GaAs at 77 K," in Proc. 7th Biennial Cornell Conference Active Microwave Devices and Circuits, Ithaca, NY, USA, pp. 389-400, August 1979.

- [34] M. S. Shur and L. F. Eastman, "Ballistic transport in semiconductors at low-temperatures for low power high speed logic," IEEE Transactions on Electron Devices, vol. ED-26, pp. 1677-1683, November 1979.

- [35] L. Pfeiffer, K. W. West, H. L. Stormer, and K. W. Baldwin, "Electron mobilities exceeding 10 cm<sup>2</sup>/V.s in modulation-doped GaAs," Applied Physics Letters, vol. 55, no. 18, pp. 1888-1890, 1989.

- [36] K. Lee, J.-S. Choi, S.-P. Sim and C.-K Kim, "Physical understanding of low field carrier mobility in Si MOSFET inversion layer," IEEE Transactions on Electron Devices, vol. 38, no. 8, pp. 1905-1911, 1991.

Muhibul Haque Bhuyan (M'07) born in Dhaka, Bangladesh in 1974. He received the B.Sc. Engg. and M.Sc. Engg. degrees both in Electrical and Electronic Engineering (EEE) from Bangladesh University of Engineering Technology (BUET), Dhaka, Bangladesh in 1998 and 2002 respectively. Currently he is pursuing his Ph. D. in the EEE Department of BUET in the field of MOS device modeling.

From July 2005 to August 2008, he led the Department of Electronics and Telecommunication Engineering of Daffodil International University (DIU)

as Head of the Department and played a pioneering role in establishing the Department of Electrical and Electronic Engineering in DIU. At present, he is working as an Assistant Professor in the Department of Electrical and Computer Engineering (ECE) of Presidency University since June 2010. He worked as a Faculty Member in the Department of ECE/EEE under the Faculty of Engineering of American International University Bangladesh (AIUB) from June 1999 to June 2003. He was with the Ultra-Scaled Devices Engineering Laboratory under the Center of Excellence (COE) program of Hiroshima University, Japan as a Researcher from July 2003 to March 2004. He also worked as a Part-time Lecturer in the Department of EEE of Ahsanullah University of Science and Technology, Bangladesh and as an Adjunct Assistant Professor in the Department of CSE of East West University, Bangladesh. His research interest includes modeling of the pocket implanted n-MOSFET and SOI-MOSFET, power electronics and control systems design using PLC, microcontroller, DSP, FPGA etc. He has more than 30 national and international journal and conference papers.

Mr. Bhuyan is also the Secretary of IEEE Bangladesh Section and also the Executive Member of Bangladesh Electronics Society (BES) and the Life Member of Institute of Engineers Bangladesh (IEB).

Quazi Deen Mohd Khosru received the B.Sc. degree in electrical and electronic engineering from Aligarh Muslim University, Aligarh, India, in 1986, the M.Sc. degree in Electrical and Electronic Engineering from Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, in 1989, and the Ph.D. degree in Electronic Engineering from Osaka University, Osaka, Japan, in 1994.

He was with the NCR Corporation, Bangladesh for a short period after graduation. He joined the Department of Electrical and Electronic Engineering,

Bangladesh University of Engineering and Technology, as a Lecturer in July 1987 and became a Professor in May 2000. He was an Associate of the Abdus Salam International Center for Theoretical Physics, Trieste, Italy, for a period of six years from January 1996 to December 2001. He was a Visiting Research Scholar at Tohoku University, Sendai, Japan, during 1999-2000 and a Visiting Professor at the Research Center for Nanodevices and Systems, Hiroshima University, Hiroshima, Japan, during 2000-2002. His research interests include nanodevice reliability, high-k gate dielectrics, hot-carrier-induced degradation, and physics, modeling and characterization of ultrathin oxide single- and double-MOS devices.

Dr. Khosru is currently the Chair of the IEEE Electron Devices Society Bangladesh Section and was the Chair of the IEEE Bangladesh Section in the year 2007.