# Doping Profile Measurement and Characterization by Scanning Capacitance Microscope for Pocket Implanted Nano Scale n-MOSFET

Muhibul Haque Bhuyan, *Member, IEEE*, Farseem Mannan Mohammedy, *Member, IEEE* and Quazi Deen Mohd Khosru, *Member, IEEE*

Abstract—This paper presents the doping profile measurement and characterization technique for the pocket implanted nano scale n-MOSFET. Scanning capacitance microscopy and atomic force microscopy have been used to image the extent of lateral dopant diffusion in MOS structures. The data are capacitance vs. voltage measurements made on a nano scale device. The technique is nondestructive when imaging uncleaved samples. Experimental data from the published literature are presented here on actual, cleaved device structures which clearly indicate the two-dimensional dopant profile in terms of a spatially varying modulated capacitance signal. Firstorder deconvolution indicates the technique has much promise for the quantitative characterization of lateral dopant profiles. The pocket profile is modeled assuming the linear pocket profiles at the source and drain edges. From the model, the effective doping concentration is found to use in modeling and simulation results of the various parameters of the pocket implanted nano scale n-MOSFET. The potential of the technique to characterize important device related phenomena on a local scale is also discussed.

*Keywords*—Linear Pocket Profile, Pocket Implanted n-MOSFET, Scanning Capacitance Microscope, Atomic Force Microscope.

# I. INTRODUCTION

S MOSFETs are scaled down in to the nano scale regime, the two-dimensional (2-D) distribution of dopants becomes a very important factor affecting their performance. For example, the revers short channel effect (RSCE) [1], believed to be caused by the enhanced diffusion of dopants near the source/drain junction regions [1]-[3], is a 2-D problem that directly affects device characteristics. Moreover, recent development of devices having lateral doping features in the channel and source/drain regions, such as, pockets or halos [4],[5] also require an understanding of how dopants diffuse in 2-D during the fabrication process. A technique that allows one to obtain the 2-D doping profile of advanced MOS devices is therefore essential. Applications include process calibration, process monitoring, process troubleshooting as well as device design and optimization. Characterization is a

Muhibul Haque Bhuyan is a Ph.D. candidate in the Department of Electrical and Electronic Engineering (EEE) of Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh. He is also with the Department of Electrical and Computer Engineering, Presidency University, Banani, Dhaka, Bangladesh. E-mail: muhibulhb@gmail.com

Farseem Mannan Mohammedy is with the Department of Electrical and Electronic Engineering (EEE) of Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh. E-mail: farseem@eee.buet.ac.bd

Quazi Deen Mohd Khosru is with the Department of Electrical and Electronic Engineering (EEE) of Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh. E-mail: qdmkhosru@eee.buet.ac.bd Manuscript received June 30, 2011; revised July 14, 2011.

follow-on activity to model development and implementation. Similarly, design verification is a follow-on activity to the design process and can be viewed as validating models developed and implemented during an earlier design phase. A number of techniques that determine one-dimensional (1-D) doping profiles have been developed and are widely used. Among these are the various capacitance-voltage (C-V) methods [6] and secondary ion mass spectroscopy (SIMS) [7]. But SIMS is destructive and time consuming. Indirect techniques include inverse modeling where a doping profile is found in such a way that its electrical behaviour obtained through numerical simulations, matches with experimental data [8]-[10]. The use of C-V data to extract 2-D doping profiles has been reported [8],[9]. But due to the extremely small dimensions and capacitance of modern submicron devices, special test structures are needed. Noise and parasitic capacitance also become important issues. However, scanning capacitance microscopy (SCM) is a direct technique that can determine the 2-D doping profiles combined with atomic force microscopy (AFM). This is one of the most powerful methods for the characterization of semiconductor devices due to its non-destructive technique and high spatial resolution. Channel length of 0.15 micron MOSFETs were determined directly for the first time using SCM [11]. Present-day VLSI device technology demands accurate knowledge of the spatial extent in three dimensions (3-D) of active impurity dopants which have been incorporated into the discrete device elements. The active region of a MOSFET device is engineered by incorporating dopants, such as, As, B, or P, in a concentration range of  $10^{15}$  to  $10^{20}$  $cm^{-3}$ . In the (2-D) junction regions of a submicron MOSFET device, it is necessary to quantify the variation (or "profile") of these impurity dopants to resolution of 100 nm or less over four orders of magnitude in concentration. Achieving such high precision in the characterization of dopant profiles is a nontrivial task in both the design and manufacturing phases.

Thus, it is desirable to have a method capable of measuring dopant profiles in 2-D (or even 3-D) in a straightforward, reliable, and repeatable (nondestructive) fashion. Lateral dopant profiles have been inferred from device capacitance measurements and simulation [12], or from junction-staining [13]. A "tomographic" technique based on a matrix of SIMS measurements has been explored [14]. In this paper, we have presented a technique using scanning capacitance microscopy (SCM) and its cousin, atomic force microscopy (AFM), which satisfies many of the desired criteria for 2-D and in some

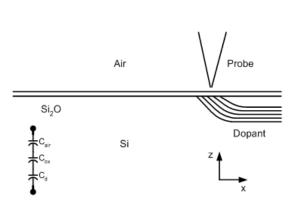

Fig. 1. Illustration of the basic concept of scanning capacitance microscopy

sense 3-D dopant imaging [15], [16]. It is noted that other workers have used scanning tunnelling microscopy (STM) for potentiometry on p-n junctions [17], [18].

## II. SCANNING CAPACITANCE MICROSCOPY

Scanning capacitance microscopy (SCM) has been commonly used to image dopant gradients in silicon and other semiconductors. As a mobile, high-resolution (to 2 nm) metaloxide-semiconductor (MOS) probe, SCM also is a nondestructive, contact less tool with which to examine local variations in dielectric thin film quality and local variations in semiconductor substrate properties. Virtually any measurement that can be made with fabricated metal electrodes can also be made with SCM. We describe here mainly the SCM; the AFM implementation is discussed briefly. As depicted in Fig. 1, a small metallic probe, with a radius of curvature at its tip of typically 50 nm, is scanned over a nonuniformly doped sample. A bias voltage (dc or ac) is placed on the tip, and the local capacitance, C, or its derivative,  $\partial C/\partial V$ , are then measured as a function of lateral position (x). The measured capacitance or capacitive gradient, as a function of bias voltage, provides a direct measurement of the activated dopant density with high spatial resolution. The inset to Fig. 1 represents the simplest equivalent circuit model for the SCM-semiconductor system. This is a series capacitance stack wherein the dopant affects the detected capacitance by virtue of dictating what the local depletion capacitance,  $C_d$ , is at lateral scan position, x.  $C_{air}$  and  $C_{ox}$ , are the capacitances due to the air gap and oxide film respectively.

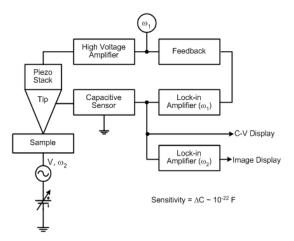

Figure 2 is a high level block diagram of the SCM. The central feature of the detection system is the capacitance sensor [19]. This sensor is basically a microwave inductance strip in a resonant circuit. It can measure capacitance variations between the tip and the sample of the order of  $10^{-22}$  F/Hz<sup>1/2</sup>. The tip scan is controlled by a feedback loop which maintains the capacitive signal constant. The piezo-scanners have a 6 mm lateral and 3 mm vertical range. To avoid low-frequency drifts caused by stray capacitances, a vertical dither is placed on the tip/sample spacing typically at 30 KHz. This also provides a means to measure the capacitive gradient.

The ac signal is filtered and rectified by the lock-in amplifier with frequency,  $\omega_1$  as shown in Fig. 2. The lock-in amplifier's

Fig. 2. Block diagram of the SCM apparatus with sample at bias voltage, V and with ac signal source having frequency,  $\omega_2$

output is sent to an integrating feedback loop to maintain the constant ac signal by adjusting the average tip height above the sample. Such a system has achieved 25 nm resolution in topographic mode [20].

In the AFM implementation [16], a laser heterodyne detection system is used to measure excursions of a cantilever-style tip which is mechanically oscillated near its resonance. These deviations are directly proportional to tip-to-sample forces, including the Coulomb force due to mutual capacitance. A signal generator provides an ac and/or dc signal between tip and sample at the desired frequency,  $\omega_2$ . Thus, a C-V curve can be taken at any given lateral position, or  $\partial C/\partial V$  curves at constant dc bias can be acquired as the tip is scanned. Both the tip scan and data acquisition are controlled by a laboratory computer. In either SCM or AFM mode, a separate laser (633 nm) is used as an optical carrier pump to obtain transport data.

# III. EXPERIMENTAL PROCEDURE

## A. Sample Preparation

Measurements have been made on a variety of VLSI structures: diffusion gratings, submicron MOSFET structures, and even DRAM devices. In this work, we describe data taken on uncleaved gratings and on cleaved MOSFETs. The gratings were prepared to emulate typical MOSFET source/drain diffusion pockets. P-type silicon substrates were thermally oxidized to grow 24 nm of SiO2. The wafers were masked with 500-nm photoresist with an 8  $\mu m$  period. A 50 KeV BF<sub>2</sub> implant at 10<sup>15</sup> cm<sup>-3</sup> dose was performed, producing a peak concentration of roughly 10<sup>20</sup> cm<sup>-3</sup> near the surface of the unmasked regions. The photoresist was stripped, leaving a topographically flat, nonuniformly implanted silicon surface. A 900°C, 10 min anneal was performed to activate (and diffuse) the dopant. The 8  $\mu$ m period was chosen in this case to minimize the effects of possibly large lateral depletion at some tip biases. Small area sections containing the gratings (typically a few square mm) were cut from the wafer and mounted on the SCM stage with the sectioned wafer surface up. The MOSFET samples were actual production devices from IBM's 1 Mb DRAM. A small section of the wafer was

cleaved to expose a MOSFET cross section. The section was mounted with the cleaved face up on the stage.

#### B. Measurement

For both the grating and the MOSFET samples, measurements were made in ambient air. An atomic force microscope is used to position a nanometer scale tip on the silicon surface, and the local capacitance change is measured as a function of the applied voltage V. We used a commercial SCM of Digital Instruments (Dimension 3100), which is a contact-mode atomic force microscope (AFM) with a 915 MHz tuned circuit to which it is coupled to the tip-sample capacitance to obtain the images [21]. SCM measurement is done in constant voltage change (constant dV) mode by applying a 100 KHz AC voltage of about 1 V to the sample. The system is configured to measure  $\partial C/\partial V$ , which depends on the variation of silicon capacitance  $(C_{Si})$  due to dopant distribution. In general, when the probe of a conductive scanning probe microscope (SPM) contacts a silicon surface through an insulating layer, a flatband offset occurs because of the movement of carriers from the insulating layer to the conductive SPM probe. Because of this flat-band offset, the magnitude of the SCM signal in the vicinity of the p-n junction does not reflect the carrier density [22]. The flat-band offset can be compensated for by applying a DC offset voltage to the sample. In principle, by applying a DC offset voltage, the change in capacitance due to the accumulation and depletion caused by the applied AC voltages can be maximized. However, the magnitude of the SCM signal varies in proportion to this change. Therefore, in this work, the level of the applied DC voltage is set according to the magnitude of the SCM signal. The SCM instrument can acquire SCM images in the amplitude mode and the phase mode, which reveals whether the carriers are n-type or ptype. The lock-in amplifier used to measure the SCM output operates at the same frequency as the frequency of the applied AC voltage. In the phase mode, the phase of the lock-in has to be designated. When the correct phase is selected, whenever, there is a change of carrier type, the lock-in amplifier output changes polarity. In the experiment, the phase is adjusted to around 900 to obtain the best contrast in the SCM images. SIMS measures the impurity distribution to a resolution of a few nm beneath the silicon surface. Our calibration of twodimensional SCM data is based on the one-dimensional SIMS data. Therefore, to acquire the exact dopant profile in the ultra shallow region, SIMS measurement is carried out at energy below 1 KeV.

# IV. MEASURED CAPACITANCE DATA

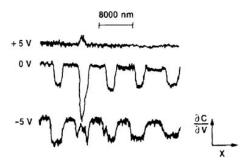

For the grating structure, Fig. 3 shows data vs. lateral scan position, x, for three typical tip-to-sample dc biases. The line traces clearly indicate the dopant variation in the sample on a scale less than 1  $\mu$ m. The periodic variation is 8  $\mu$ m. The signal varies strongly with bias voltage as expected from the simple model based on depletion capacitance in the semiconductor. The largest signal is apparent in the lightly-doped (p-type) region, due to the fact that depletion capacitance varies more rapidly with bias at lower dopant densities. Note

Fig. 3. Three line scans of the grating structure showing the  $\partial C/\partial V$  signal at different bias voltages

that there is some defect or nonuniformity in the fourth period of the data which has apparently shifted the depletion voltage. Since the sample surface was measured in topographic mode to be nearly atomically flat, this defect is evidently some fixed charge, perhaps in the oxide.

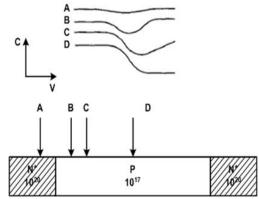

Figure 4 shows a set of C-V curves taken with the SCM tip held fixed while positioned over several points along the grating structure. When the tip is centered over the relatively low-doped region (position D), the C-V curve looks like a typical high-frequency C-V curve. As the tip is moved closer to the junction near the more highly doped n-type region, the C-V curves are altered from the usual 1-D form. A gradual transition is evident as the junction is approached, due to the mixing of lateral depletion effects in this region of highly inhomogeneous doping. At positions A, B and C, the signature of both p- and n-type dopant are evident (positive and negative C-V slope, respectively). When the tip is well inside the highly-doped n-type region (i.e., to the left of position A), a signal is measured but cannot be displayed on the scale of Fig. 4.

A first-order deconvolution of the  $\partial C/\partial V$  vs. x data to obtain crude contours of activated dopant density in 2-D is possible by a simple extension of the standard C-V analysis [23]. One integrates the  $\partial C/\partial V$  vs. data (e.g. the data of Fig. 3) to obtain C(V) at x within a constant. A less efficient procedure requires measuring both a  $\partial C/\partial V$  vs. x and C(V) vs. x, as in Fig. 4, to avoid the integration procedure. The modified standard model yields an expression for the local

Fig. 4. Local C-V measurements acquired on grating structure with tip stationary at various points

ISSN: 2517-9438

Vol:5, No:8, 2011

2-D dopant profile of grating structure. Upper profile is process simulation and lower profile is deconvolved from SCM data

activated dopant density,  $N_{sub}(x, z)$ , where z is the vertical dimension (in the bulk).

$$N_{sub}(x,z(x)) = -\frac{q\varepsilon_{Si}}{C^{-3}(a;V)/\partial C/\partial V}$$

(1)

,where q is the electronic charge,  $\varepsilon_{Si}$  is the dielectric coefficient for silicon. It is important to note that z is interpreted as the local depletion depth given by equation 2.

$$z(x) = \varepsilon_{Si} \left( \frac{1}{C(a;V)} - \frac{1}{C_{ox}} - \frac{1}{C_{air}} \right)$$

(2)

The parameter a, which appears in C(a; V), is necessary to scale the integrated, measured signal. a is unit less and of the order of unity (0.3 in this case); it is interpreted as dependent on the effective spot size which the tip presents to the sample.

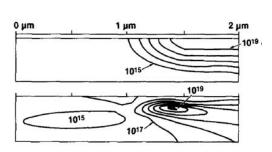

Figure 5 shows the results of such a deconvolution for data taken on the grating structure near one of the junction regions. The contours of dopant density in the upper plot are the result of a process simulation of the steps required to create the sample structure. The contours in the lower plot are the deconvolution of data such as shown in Fig. 3. The agreement is admittedly gross, but is encouraging since it indicates that the data have some quantitative value. Much of the error in the deconvolution is attributed to the neglect of junction capacitance and to the assumption of a homogeneous depletion front near the tip.

## V. POCKET DOPING PROFILE

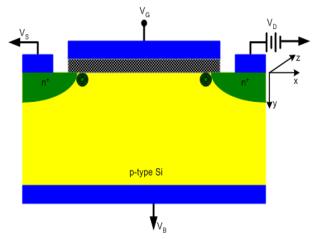

The pocket implanted n-MOSFET structure shown in Fig. 6 is considered in this work and assumed co-ordinate system is shown at the right side of the structure. Localized extra dopings are shown by circles near the source and drain side regions. All the device dimensions are measured from the oxide-silicon interface. In the structure, the junction depth  $(r_i)$  is 25 nm. The oxide thickness  $(t_{ox})$  is 2.5 nm, and it is  $SiO_2$  with fixed oxide charge density of  $10^{11}$  cm<sup>-2</sup>. Uniformly doped p-type Si substrate is used with doping concentration  $(N_{sub})$  of  $4.2 \times 10^{17}$  cm<sup>-3</sup> with pocket implantation both at the source and drain side with peak pocket doping concentration of  $1.75 \times 10^{18}$  cm<sup>-3</sup> and pocket lengths from 20 to 30 nm, and source or drain doping concentration of  $9.0 \times 10^{20}$  cm<sup>-3</sup>.

The pocket implantation, which causes the Reverse Short Channel Effect (RSCE), is done by adding impurity atoms

Fig. 6. Pocket implanted n-MOSFET structure

both from the source and drain edges. It is assumed that the peak pocket doping concentration  $(N_{pm})$  gradually decreases linearly towards the substrate level concentration  $(N_{sub})$  with a pocket length  $(L_p)$  from both the source and drain edges.

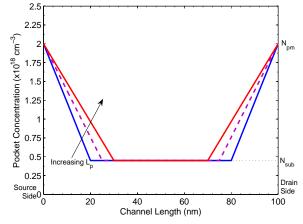

Fig. 7. Simulated pocket profiles at the surface for different pocket lengths,  $\frac{1}{2}$  $L_p = 20$ , 25 and 30 nm; peak pocket concentration,  $N_{pm} = 2.0 \times 10^{18}$  cm<sup>-2</sup>

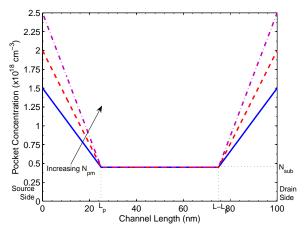

Fig. 8. Simulated pocket profiles at the surface for various peak pocket concentrations,  $N_{pm}=1.5\times10^{18},\ 2.0\times10^{18},\ 2.5\times10^{18}\ {\rm cm^{-3}};$  pocket length,  $L_p = 25 \text{ nm}$

The basis of the model of the pocket is to assume two laterally linear doping profiles from both the source and drain edges across the channel as shown in Figs. 7-8 for substrate concentration of  $4.2\times10^{17}~{\rm cm^{-3}}$  and channel length of 100 nm. The pocket parameters,  $N_{pm}$  and  $L_p$ , play important role in determining the RSCE. At the source side, the pocket profile is given as

$$N_s(x) = -\frac{N_{pm} - N_{sub}}{L_p}x + N_{pm}$$

$$N_s(x) = N_{sub} \frac{x}{L_p} + N_{pm} \left( 1 - \frac{1}{L_p} x \right)$$

(3)

At the drain side, the pocket profile is given as

$$N_d(x) = \frac{N_{pm} - N_{sub}}{L_p} [x - (L - L_p)] + N_{sub}$$

$$N_d(x) = N_{sub} \left( \frac{L}{L_p} - \frac{1}{L_p} \right) + N_{pm} \left( 1 - \frac{L}{L_p} + \frac{1}{L_p} x \right)$$

(4)

,where x represents the distance across the channel. Since these pile-up profiles are due to the direct pocket implantation at the source and drain sides, the pocket profiles are assumed symmetric at both sides.

With these two conceptual pocket profiles of equations (3) and (4), the profiles are integrated mathematically along the channel length from the source side to the drain side and then the integration result is divided by the channel length (L) to derive an average effective doping concentration  $(N_{eff})$  as shown in equation (5).

$$N_{eff} = \frac{1}{L} \int_0^L \left[ N_s(x) + N_d(x) + N_{sub} \right] \mathrm{d}x \tag{5}$$

Putting the expressions of  $N_s(x)$  and  $N_d(x)$  from equations (3) and (4) in equation (5) the effective doping concentration is obtained in equation (6).

$$N_{eff} = N_{sub} \left( 1 - \frac{L_p}{L} \right) + \frac{N_{pm} L_p}{L} \tag{6}$$

This effective doping concentration expression is then used in deriving the surface potential model by applying Gauss's law [25]. This surface potential model is used to find the inversion layer charges and other parameters for determining the effective inversion layer mobility. When  $L_p \ll L$  for long channel device then the pocket profile has very little effect on uniform substrate concentration at the surface, but when  $L_p$  is comparable with L then the pocket profile parameters affects the substrate doping concentration at the surface of the n-MOSFET. This causes the surface potential, threshold voltage and hence effective mobility and subthreshold drain current along with other parameters of pocket implanted n-MOFET to change due to RSCE.

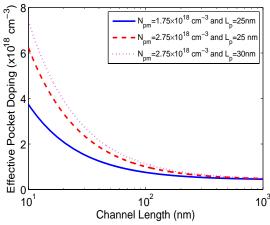

Because of the pocket implantation, effective doping concentration increases with decreasing channel lengths as observed in Fig. 9. This becomes stronger when both peak pocket concentration and/or pocket length increases.

Fig. 9. Simulated effective pocket doping concentration vs. channel lengths at the surface for different peak pocket concentration and pocket lengths with substrate concentration,  $N_{sub}=4.5\times10^{17}~{\rm cm}^{-3}$

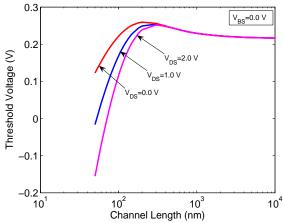

Fig. 10. Threshold voltage vs. channel length curves along the channel for various drain bias,  $V_{DS}=0.0~{

m V}$  with  $V_{BS}=0.0~{

m V}$

## VI. SIMULATED RESULTS AND DISCUSSIONS

In order to verify the proposed linear pocket profile model, various operational parameters, such as, threshold voltage, surface potential, mobility, drain current etc. have been simulated using this pocket profile model. Few simulation results are shown in this section. Fig. 10 shows the threshold voltage variation as a function of channel length for different drain bias voltages. As the channel length goes down for particular drain bias, threshold voltage increases first and then with further decrement of channel length threshold voltage reduces, i.e. it shows both RSCE and SCE. But as the drain bias increases, both RSCE and SCE occur at longer channel length due to the drain induced barrier lowering (DIBL). As channel length becomes shorter DIBL effect is more pronounced, electric field is very high and it lowers the potential barrier that separates it from the adjacent diffused junction [24].

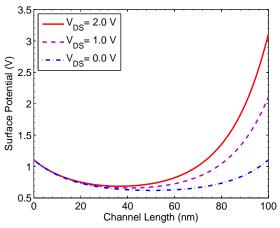

Figure 11 shows the variation of surface potential along the channel for different drain biases. It has been observed that as the drain bias increases surface potential increases at the drain

Fig. 11. Surface potential vs. channel length for various drain biases with channel length, L=100 nm and substrate bias,  $V_{BS}=0.0=0.0~\rm V$

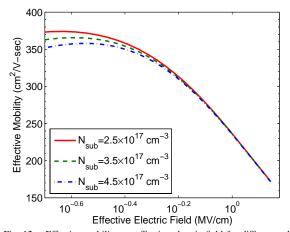

Fig. 12. Effective mobility vs. effective electric field for different substrate concentrations ( $N_{sub}$ ) with  $L=0.1~\mu\text{m},~N_{pm}=1.75\times10^{18}~\text{cm}^{-3},~L_p=25~\text{nm},~V_{DS}=0.05~\text{V},~T=300~\text{K}$

side whereas it remains constant at the source side. Because, at the drain end carriers are then depleted [25].

Figure 12 shows the variation of effective mobility vs. effective normal electric field for different values of substrate concentration. It has been observed that there is no change in the curve with the change in substrate concentration. This proves the universality of mobility curve [26].

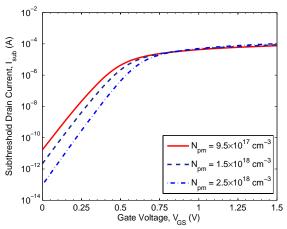

In order for the further verification of the proposed model, subthreshold drain current model is simulated incorporating the proposed effective mobility model. The model is simulated for three different pocket doses as shown in Fig. 13. It is observed that the subthreshold drain current behavior with the gate voltage variation is same as observed in [27]. As the pocket dose is increased the subthreshold drain current is decreased for a particular gate bias due to the This happens due to the additional doping atoms present near the source and drain edges and hence the increase of the Coulomb scattering rate and consequent mobility degradation. Also with the decrement of peak pocket implant concentration,

Fig. 13. Subthreshold drain current versus gate voltage for for different peak pocket implant concentrations with drain bias,  $V_{DS}=0.05~\rm V$ , substrate concentration,  $N_{sub}=4.5\times 10^{17}~\rm cm^{-3}$ , pocket length,  $L_p=25~\rm nm$  and channel length  $L=100~\rm nm$

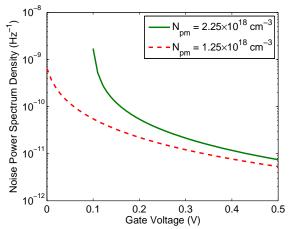

Fig. 14. Noise power spectrum density vs. gate voltage for two pocket doses with L=50 nm,  $L_p=25$  nm,  $V_{DS}=0.2$  V, f=100 Hz

subthreshold slope decreases since RSCE diminishes [27].

Fig. 14 shows the noise power spectrum density variations with the gate length for two different pocket doses at gate and drain bias of 0.5 V and 0.2 V respectively. Noise degradation is more significant in shorter channel length device as pocket implant region is comparable with the channel length of the device. For longer channel length, the noise is not changed with the increment of the pocket implantation dose [28].

#### VII. CONCLUSION

Lateral dopant profiling has been demonstrated on a 100-nm scale by a straightforward, basically non-destructive technique. With increased sensitivity, imaging on a 10-nm scale is believed feasible. Other important measurements can evidently be made, including trapped-charge, surface-defects, direct measurement of a variety of device-scale capacitances and, perhaps, carrier transport. It is anticipated that, with moderate enhancement, characterization of VLSI devices using SCM or AFM will have much value in future device development and manufacture. Based on the characterized dopant profile,

a linear pocket profile is assumed both at the source and drain sides. Then the simulated pocket profile is presented and simulated threshold voltage, surface potential and subthreshold drain current models developed using the effective pocket doping concentration are presented to show the usefulness of the assumed pocket profiles.

#### ACKNOWLEDGMENT

The authors would like to acknowledge the financial support provided by the Department of Electrical and Electronic Engineering (EEE), Bangladesh University of Engineering and Technology (BUET) for conducting the research work.

#### REFERENCES

- [1] M. Nishida and H. Onodera, "An anomalous increase of threshold voltage with shortening the channel lengths for deeply boron-implanted n-channel MOSFETs," IEEE Transactions on Electron Devices, vol. 48, pp. 1101, 1981.

- [2] M. Orlowski, C. Mazure, and F. Lau, "Submicron short-channel effects due to gate reoxidation induced lateral interstitial diffusion," in IEEE IEDM Technical Digest, 1987, pp. 87-632.

- [3] C. Rafferty, H. Vuong, S. Eshraghi, M. Giles, M. Pinto, and S. Hillenius, "Explanation of reverse short-channel effect by defect gradients," in IEEE IEDM Technical Digest, 1993, pp. 93-311.

- [4] G.G. Shahidi, J. Warnock, S. Fischer, P. A. McFarland, A. Acovic, S. Subbanna, E. Ganin, E. Crabbe, J. Comfort, J. Y.-C. Sun, T. H. Ning, and B. Davari, "High-performance devices for a 0.15-μm CMOS technology," IEEE Electron Device Letters, vol. 14, pp. 466-468, Oct. 1993.

- [5] B. Yu, C. H. J. Wann, E. D. Nowak, K. Noda, and C. Hu, "Short-channel effect improved by lateral channel-engineering in deep-submicronmeter MOSFET's," IEEE Transactions on Electron Devices, vol. 44, pp. 627-634, April 1997.

- [6] S. M. Śze, "Physics of Semiconductor Devices," 2nd Edition, John Wiley and Sons, New York, ch. 8, 1981.

- [7] P. C. Zalm, "The application of dynamic SIMS in silicon semiconductor technology," Philips Journal of Research, vol. 47, nos. 3-5, pp. 287-302, 1993.

- [8] G. J. L. Ouwerling, "A problem-specific inverse method for twodimensional doping profile determination from capacitance-voltage measurements" Solid State Electronics, vol. 34, no. 2, pp. 197, 214, 1991

- ments," Solid State Electronics, vol. 34, no. 2, pp. 197-214, 1991.

[9] N. Khalil, J. Faricelli, D. Bell, and Selberherr, "The extraction of two-dimensional MOS transistor doping via inverse modeling," IEEE Electron Device Lett., vol. 16, pp. 17-19, Jan. 1995.

- [10] Z. K. Lee, M. B. McIlrath and D. A. Antoniadis, "Two dimensional doping profile characterization of MOSFET's by inverse modeling using I-V characteristics in the subthreshold region," IEEE Transactions on Electron Devices, vol. 46, pp. 1640-1649, Aug. 1999.

- [11] R. N. Kleiman, M. L. O'Malley, F. H. Baumann, J. P. Garno and G. L. Timp, "Junction delineation of 0.15 m MOS devices using scanning capacitance mircoscopy," in IEDM Technical Digest, 1997, pp. 691-694.

- [12] W. Rosner, W. Hansch, B. Moore, M. Orlowski, A. Spitzer, and C. Werner, DRC Proceedings, p. 9, 1990.

- [13] S. T. Ahn and W. A. Tiller, Journal of Electrochemical Society, vol. 135, p. 2370, 1988.

- [14] S. H. Goodwin-Johnson, R. Subrahmanyan, C.E. Floyd and H. Z. Massoud, "Two-dimensional impurity profiling with emission computed tomography techniques," IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, vol. 8, no. 4, pp. 323-335, 1989.

- [15] C.C. Williams, J. Slinkman, W.P. Hough, and H.K. Wickramasinghe, "Lateral dopant profiling with 200 nm resolution by scanning capacitance microscopy," Applied Physics Letters, Vol. 55, no.16, p. 1662-1664, Oct. 1989.

- [16] D. W. Abraham, C. Williams, J. Slikman, and H. K. Wickramasinghe, "Lateral dopant profiling in semiconductors by force microscopy using capacitive detection," Journal of Vacuum Science and Technology, vol. B9, pp. 703, 1991.

- [17] S. Hosaka, S. Hosoki, K. Takata, K. Horiuchi, and N. Natsuaki, "Observation of pn junctions on implanted silicon using a scanning tunneling microscope," Applied Physics Letters, vol. 53, pp. 487, 1988.

- [18] S. Kordic, E.J. Van Loenon, D. Dijkkamp, A.J. Hoeven and H.K. Moraai, "Scanning tunneling microscopy on cleaved silicon pn junctions," IEEE IEDM Technical Digest, pp. 277-280, 1989.

- [19] J. R. Matey and J. Blanc, "Scanning capacitance microscopy," Journal of Applied Physics, vol. 57, no. 5, pp. 1437-1444, 1985.

- [20] C. C. Williams, W. P. Hough and S. A. Rishton, "Scanning capacitance microscopy on a 25 nm scale," Applied Physics Letters, vol. 55, pp. 203 - 205, 1989.

- [21] Y. Huang and C. C. Williams, "Capacitance-voltage measurement and modeling on a nanometer scale by scanning C-V microscopy," Journal of Vacuum Science and Technology B: Microelectronics and Nanometer Structures, vol. 12, no. 1, pp. 369-372, 1994.

- [22] H. Edwards, R. McGlothlin, R. S. Martin, Elisa U, M. Gribelyuk, R. Mahaffy, C. K. Shih, R. S. List and V. A. Ukraintsev, "Scanning Capacitance Spectroscopy: An analytical technique for p-n junction delineation in Si devices," Applied Physics Letters vol. 72, 1998, pp. 698-700.

- [23] W. Van Gelder and E.H. Nicollian, "Silicon impurity distribution as revealed by pulsed MOS C-V measurements," Solid State Science, Journal of Electrochemical Society, vol. 118, p. 138-141, 1971.

- [24] M. H. Bhuyan and Q. D. M. Khosru, "Linear pocket profile based threshold voltage model for sub-100 nm n-MOSFET incorporating substrate and drain bias effects," in Proc. of the 5th International Conference on Electrical and Computer Engineering (ICECE 2008), 20-22 December 2008, Dhaka, Bangladesh, pp. 447-451.

- [25] M. H. Bhuyan and Q. D. M. Khosru, "Linear profile based analytical surface potential model for pocket implanted sub-100 nm n-MOSFET," Journal of Electron Devices, France, ISSN 1682-3427, vol. 7, 2010, pp 235-240.

- [26] M. H. Bhuyan and Q. D. M. Khosru, "Inversion layer effective mobility model for pocket implanted nano scale n-MOSFET," International Journal of Electrical and Electronics Engineering, ISSN 2010-3972, vol. 5, no. 1, Januay 2011, pp. 50-57.

- [27] Muhibul Haque Bhuyan and Q. D. M. Khosru, "An Analytical Subthreshold Drain Current Model for Pocket Implanted Nano Scale n-MOSFET," Journal of Electron Devices, France, ISSN 1682-3427, vol. 8, October 2010, pp. 263-267.

- [28] M. H. Bhuyan and Q. D. M. Khosru, "Low frequency drain current flicker noise model for pocket implanted nano scale n-MOSFET," in Proc. of the IEEE Nanotechnology Materials and Devices Conference (NMDC 2010), 12-15 October 2010, California, USA, pp. 295-299.

Muhibul Haque Bhuyan (M'07) born in Dhaka, Bangladesh in 1974. He received the B.Sc. Engg. and M.Sc. Engg. degrees both in Electrical and Electronic Engineering (EEE) from Bangladesh University of Engineering Technology (BUET), Dhaka, Bangladesh in 1998 and 2002 respectively. Currently he is pursuing his Ph. D. in the EEE Department of BUET in the field of MOS device modeling.

From July 2005 to August 2008, he led the Department of Electronics and Telecommunication Engineering of Daffodil International University (DIU)

as Head of the Department and played a pioneering role in establishing the Department of Electrical and Electronic Engineering in DIU. At present, he is working as an Assistant Professor in the Department of Electrical and Computer Engineering (ECE) of Presidency University since June 2010. He worked as a Faculty Member in the Department of ECE/EEE under the Faculty of Engineering of American International University Bangladesh (AIUB) from June 1999 to June 2003. He was with the Ultra-Scaled Devices Engineering Laboratory under the Center of Excellence (COE) program of Hiroshima University, Higashi-Hiroshima, Japan as a Researcher from July 2003 to March 2004. He also worked as a Part-time Lecturer in the Department of EEE of Ahsanullah University of Science and Technology, Bangladesh and as an Adjunct Assistant Professor in the Department of CSE of East West University, Bangladesh. His research interest includes modeling of the pocket implanted n-MOSFET and SOI-MOSFET, power electronics and control systems design using PLC, microcontroller, DSP, FPGA etc. He has around 40 national and international journal and conference papers.

Mr. Bhuyan was the Secretary of IEEE Bangladesh Section. Now he is the Executive Committee Member of Bangladesh Electronics Society (BES), Life Member of the Institute of Engineers Bangladesh (IEB) and Member of IEEE and EDS.

Farseem Mannan Mohammedy received the B.Sc. Engg. and M.Sc. Engg. degrees both in Electrical and Electronic Engineering (EEE) from Bangladesh University of Engineering Technology (BUET), Dhaka, Bangladesh in 1999 and 2002 respectively, and the Ph.D. degree in Electrical Engineering from McMaster University, Hamilton, Ontario, Canada in 2008.

He is currently an Assistant Professor with the Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technol-

ogy, where he has been working since 1999.

His research interests include III-V semiconductor growth and fabrication, focusing on antimonide materials. He is also interested in the modeling and fabrication of novel photodetector structures and antimony-based solar cells, nanotechnology and renewable energy sources.

Quazi Deen Mohd Khosru received the B.Sc. degree in electrical and electronic engineering from Aligarh Muslim University, Aligarh, India, in 1986, the M.Sc. degree in Electrical and Electronic Engineering from Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, in 1989, and the Ph.D. degree in Electronic Engineering from Osaka University, Osaka, Japan, in 1994.

He was with the NCR Corporation, Bangladesh for a short period after graduation. He joined the Department of Electrical and Electronic Engineering,

Bangladesh University of Engineering and Technology, as a Lecturer in July 1987 and became a Professor in May 2000. He was an Associate of the Abdus Salam International Center for Theoretical Physics, Trieste, Italy, for a period of six years from January 1996 to December 2001. He was a Visiting Research Scholar at Tohoku University, Sendai, Japan, during 1999-2000 and a Visiting Professor at the Research Center for Nanodevices and Systems, Hiroshima University, Higashi-Hiroshima, Japan during 2000–2002. His research interests include nanodevice reliability, high-k gate dielectrics, hot-carrier-induced degradation, and physics, modeling and characterization of ultrathin oxide single- and double-gate MOS devices.

Dr. Khosru is currently the Chair of the IEEE Electron Devices Society Bangladesh Section and was the Chair of the IEEE Bangladesh Section in the year 2007.