# Evaluation of Fuzzy ARTMAP with DBSCAN in VLSI Application

K. A. Sumithradevi, Vijayalakshmi. M. N., Annamma Abraham. and Dr. Vasanta

Abstract—The various applications of VLSI circuits in high-performance computing, telecommunications, and consumer electronics has been expanding progressively, and at a very hasty pace. This paper describes a new model for partitioning a circuit using DBSCAN and fuzzy ARTMAP neural network. The first step is concerned with feature extraction, where we had make use DBSCAN algorithm. The second step is the classification and is composed of a fuzzy ARTMAP neural network. The performance of both approaches is compared using benchmark data provided by MCNC standard cell placement benchmark netlists. Analysis of the investigational results proved that the fuzzy ARTMAP with DBSCAN model achieves greater performance then only fuzzy ARTMAP in recognizing sub-circuits with lowest amount of interconnections between them The recognition rate using fuzzy ARTMAP with DBSCAN is 97.7% compared to only fuzzy ARTMAP

**Keywords**—VLSI, Circuit partitioning, DBSCAN, fuzzy ARTMAP.

# I. INTRODUCTION

ADVANCES in semiconductor technology in the integration level of integrated circuits have enhanced many features, increased the performance; improved reliability of electronic equipment, and at the same time reduced the cost, power consumption and system size. As size and complexity of digital system has increased, more computer aided design tools are introduced into hardware design processes. There is Hardware/software [3] design methodology for embedded systems that seeks to satisfy system-level constraints by exploiting the synergy between hardware and software through their concurrent design [2]. During partitioning, design components are assigned to hardware and software implementation targets. The output of

K. A. SumithraDevi is with RVCE, Visveswaraya Technological University, Head of the dept, Dept of MCA,Bangalore, India (phone:+919945004632; e-mail: sumithraka@hotmail.com)

Vasantha is with RVCE, Visveswaraya Technological University, Professor, Dept. of I.S.E, Bangalore, India (phone:+919449679696; e-mail: vasanthaprak@yahoo.com)

Vijayalakshmi M.N. is with RVCE, VisveswarayaTechnological University, Lecturer, Dept. of MCA, Bangalore, India (phone:+919986551776; e-mail:mnvijayalakshmi @rediffmail.com).

Annamma Abraham is with RVCE, Visveswaraya Technological University, Addt. Asst. Professor, Dept of MCA, Bangalore, India (phone:+919448970039; e-mail: annamma65@yahoo.co.in).

the practitioner has a significant impact on the subsequent scheduling of software. The circuit partitioning problem arises in VLSI layout. Components called cells (or nodes) are to be laid out in two or more blocks. The cells are connected by wires, called nets. Nets connect two or more cells. Cells may be connected to more than one net. The netlistis the set of all nets to be partitioned. The netlist partitioning problem is known to be NP-hard [4]. The designers extensively rely on software tools for nearly every aspect of the development cycle, from circuit specification and design entry to the performance analysis, layout generation and verification. Partitioning is a problem that runs central to VLSI design automation, and one that has attracted a great deal of interest; a recent survey [1] lists almost 200 papers on the subject. In order to reduce the complexity of the design process, several intermediate levels of abstraction are introduced. Partitioning a circuit is necessary if it is too large to be accommodated on a single chip. A number of heuristic algorithms [5, 6, 7, 8, 9, 10] have been developed over the past three decades for various physical design problems In this paper, we introduce DBSCAN algorithm for feature extraction which is capable of finding a better set of clusters that minimize the amount of investigation required and classifier as fuzzy ARTMAP to recognize the sub-circuits with lowest amount of interconnections between them.

This paper is organized as follows: In section 2, a brief introduction to the overview of the proposed system. Section 3 presents a new feature extraction method using DBSCAN algorithm that has not been used previously for Circuit partioning in VLSI with fuzzy ARTMAP classification. Section 4 explains the structure of simplified fuzzy ARTMAP based in VLSI. Experimental results are presented in section 5 and conclusions are given in section 6.

## II. OVERVIEW OF PROPOSED SYSTEM

The sample circuit of the model is bipartite. The feature extractor obtains feature vector for subcircuit, and is sent to training or inference module. The SFAM (simplified fuzzy ARTMAP) [11] has two modules, i.e. training and inference module. The feature vector of training subcircuits and the categories to which they belongs are specified to SFAM's training module. Once the training phase is complete, the vector represents the subcircuit with minimum interconnection. The test subcircuit pattern which is to be recognize with minimum interconnection is fed to inference

module. Classifications of sub circuits are done by associating the feature vector with the top-down weight vectors [12, 13] in SFAM. The system can handle both symmetric and asymmetric circuit. In symmetric pattern, only distinct portion of circuit is trained whereas in asymmetric (1/2n)th portion of circuit is considered.

# III. DBSCAN (FEATURE EXTRACTOR)

To separate the set D into subsets of similar densities Density-based algorithms is used [14]. In the best case they can find out the cluster number k routinely and categorize the clusters of random shape and size [15]. The runtime of this algorithms is in magnitude of O(n log(n)) for low-dimensional data. [16] .A density-based cluster algorithm is based on two properties given below [14].

- (1) One to define a region  $C \subseteq D$ , which forms the basis for density analyses;

- (2) Another to propagate density information (the provisional cluster label) of C

In DBSCAN a region is defined as the set of points that lie in the  $\in$ -neighborhood of some point p. if |C| exceeds a given Min Pts-threshold Cluster lab el propagation from p to the other points in C. The complete description of DBSCAN algorithm is provided in [15, 17, 18].

## IV. SIMPLIFIED FUZZY ARTMAP MODULE

The basic principle of Adaptive Resonance Theory (ART) was first introduced by Grossberg in 1976[11], whose structure resembles those of feed-forward networks. Fuzzy logic with the combination of Adaptive Resonance Theory gives Fuzzy ARTMAP is a class of neural network that perform supervised training of recognition pattern and maps in response to input vectors generated from DBSCAN algorithm [16] in this paper. Fuzzy ARTMAP [12] is a structural design which synthesize the fuzzy logic with adaptive resonance theory neural network. Fuzzy ARTMAP is two layer network containing an input and out put layer. In context of the circuit partinoning in VLSI design to recognize the subcircuit with minimum interconnection between them, the size of input layer is 4 and output layer is 10. Hence it outcomes in 2-10 layered Fuzzy ARTMAP model.

For input vector I and cluster j from DBSCAN algorithm, Choice function given by:

$$\frac{\text{CF}_{j}(I) = |I \wedge W_{j}|}{\alpha + |W_{j}|} \tag{1}$$

where  $\,\alpha$  is small constant about 0.0000001,  $W_{j}$  is top-down weight

Winner node is one with highest activation /choice function, i.e

Winner=

$$\max(CF_i)$$

(2)

Fig. 2 Core and border pixel density connectivity mapping nonlinear data to a higher dimensional feature space

Match function which is very much used to find out whether the network must adjust its learning parameters is given by

$$MF_{j}(I) = |I \wedge W_{j}|$$

$$|I|$$

(3)

If MF  $_{j}(I) \ge vigilance$  parameter  $(\rho)$  then Network is in state of resonance, where  $\rho$  is in range  $0 \le \rho \le 1$ .

If MF  $_{j}$  (I)  $\leq$  vigilance parameter ( $\rho$ ) then Network is in state of mismatch reset.

# V. RESULTS

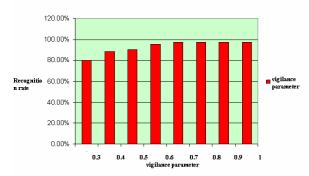

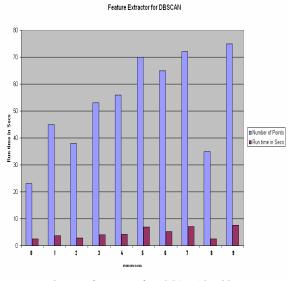

The circuit is bipartite. The feature vectors of the subcircuit are extracted by using the generic approach of DBSCAN. Extracted features from the subcircuit, the vectors are fed into the fuzzy ARTMAP and the recognition of the subcircuit with minimum interconnection between them. The table 1 depicts the time required by DBSCAN for the 10 different way of bipartite sample circuits. It depicts that as the number of points considered in the subcircuit increases, the run time for extracting the feature also increases. The Table II depicts that as the vigilance parameter increases, the recognition rate also increases. From the table, it is clear that for vigilance parameter of 0.65, the recognition rate is almost most 97.7% which is the best recognition rate for subcircuit.

TABLE I FEATURE EXTRACTOR USING DBSCAN

| Subcircuits | Number of Points | Run time in |

|-------------|------------------|-------------|

|             |                  | Secs        |

| sample #l   | 23               | 2.5         |

| Sample #2   | 45               | 3.8         |

| Sample #3   | 38               | 2.9         |

| Sample #4   | 53               | 4.1         |

| Sample #5   | 56               | 4.3         |

| Sample #6   | 70               | 6.9         |

| Sample #7   | 65               | 5.3         |

| Sample #8   | 72               | 7.2         |

| Sample #9   | 35               | 2.5         |

| Sample #10  | 75               | 7.6         |

TABLE II

UNITS FOR EFFECT OF VIGILANCE PARAMETER ON RECOGNITION RATE

| Vigilance | <b>Recognition Rate</b> |

|-----------|-------------------------|

| Parameter |                         |

| 0.21      | 80.16%                  |

| 0.32      | 88.56%                  |

| 0.43      | 90.3%                   |

| 0.56      | 95.3%                   |

| 0.65      | 97.2%                   |

| 0.75      | 97.3%                   |

| 0.85      | 97.5%                   |

| 0.87      | 97.6%                   |

Graph in Fig. 3 shows the how vigilance parameter vary recognition rate. We found that at 0.65, recognition rate remain constant i.e. 97% around. Fig. 4 shows performance of DBSCAN Algorithm.

Fig. 3 Recognition rate versus vigilance parameter

Fig. 4 Performance of DBSCAN Algorithm

## VI. CONCLUSION

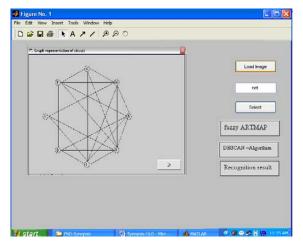

In this paper recognition of subcircuit with minimum interconnection between them is done using fuzzy ARTMAP neural network by using DBSCAN as the feature extractor. Software is simulated for eight and six nodes. Tested successfully in partitioning these nodes to arrive minimum interconnection between them .Experimental results shows that the recognition rate using DBSCAN with fuzzy ARTMAP best compared is to only ARTMAP.Classification is done at rate of better cut size using DBSCAN -fuzzy compared to ARTMAP. Fig. 5 shows the screen shots of the module use to recognize the subcircuit with minimum interconnection using DBSCAN with fuzzy ARTMAP.

Fig. 5 Screen shots of recognizer model of DBSCAN with fuzzy ARTMAP

Fig. 6 Screen shot gives a user the choice for selection of 6 or 8 nodes

Fig. 7 Screen shots shows the input for eight nodes

### REFERENCES

- C.J. Alpert and A.B. Kahng, "RecentDirections in Net list Partitioning:A Survey," Integration: the VLSIJournal, 19(1-2), 1995, pp. 1 - 81.

- [2] Giovanni De Micheli and Rajesh K. Gupta. Hardware/software codesign. Proceedings of the IEEE, 85(3):349–365, March 1997.

- [3] Jan Madsen, Jesper Grode, and Peter V. Knudsen. Hardware/Software Partitioning using the LYCOS System, chapter 9. Hardware/Software Codesign: principles and Practice. Kluwer Academic Publishers, Netherlands, 1997.

- [4] M. Garey and D. Johnson. Computers and Intractability. Freeman, 1979.

- [5] P. Chen and D. F. Wong, "On retiming for FPGA logic module minimization," Proc. IEEE Intl. Conference on Computer Design, pp.394-397, 1994.

- [6] Y. P. Chen, T. C. Wang and D. F. Wong, "A graph partitioning problem for multiple-chip design", Proc. Intl. Symposium on Circuits and Systems, May 1993.

- [7] Efficient partitioning of components, Annual ACM IEEE Design Automation Conference Proceedings of the 5th annual workshop on Design automation Washington, D. C., United States, 1968, 16.1 - 16.21.

- [8] B.W. Kernighan and S. Lin, "An Efficient Heuristic Procedure for Partitioning Graphs", The Bell System Technical Journal, vol. 49, n. 2, pp. 291–307, February1970.

- [9] C.M. Fiduccia and R.M. Mattheyses, "A Linear-Time Heuristic for Improving Network Partitions", inProceedings of > □□ \_\_DAC, pp. 175–181, Las Vegas, Nevada, June 1982, ACM/IEEE.

- [10] S. Dutt and W. Deng, "VLSI Circuit Partitioning byCluster-Removal Using Iterative Improvement Techniques", in IEEE International Conference on CAD,pp. 194–200. ACM/IEEE, 1996.

- [11] Carpenter, G.A., 1997, Distributed learning, recognition, and prediction by ART and ARTMAP neural networks, Neural Networks, 10:1473-1494

- [12] Carpenter, G.A., Grossberg, S., Markuzon, N., Reynolds, J.H., and Rosen, D.B., 1992, Fuzzy ARTMAP: neural network architecture for Incremental supervised learning of analog multidimensional maps, IEEE Transactions on Neural Networks, 3:698-713.

- [13] Caudell, T.P., Smith, S.D.G., Escobedo, R., and Anderson, M., 1994, NIRS: Large scale ART-1 neural architectures for engineering design Retrieval, Neural Networks, 7:1339-1350.

- [14] Benno Stein and Michael Busch, Second International Workshop on Text- Based information Retrieval (TIR 05)Stein, Meyer zu Eißen (Eds.)Fachberichte Informatik, pp. 45-56, ISSN 1860-4471c University of Koblenz-Landau, Germany.

- [15] Martin Ester, Hans-Peter Kriegel, Jorg Sander, Xiaowei Xu, Proceedings of 2nd International Conference on Knowledge Discovery and Data Mining (KDD-96).

- [16] Busch. Analyse dichtebasierter Clusteralgorithmen am Beispiel von DBSCAN und MajorClust. Study work, Paderborn University, Institute for Computer Science, March 2005.

- [17] Tan, S.C., Rao, M.V.C., and Lim, C.P. (2004b), "An adaptive fuzzy minmax conflict-resolving classifier," in Proceedings of the 9th Online

- World Conference on Soft Computing in Industrial Applications, WSC9, 20 September 8 October 2004.

- [18] Dagher, I, Georgiopoulos, M, Heileman, G.L., Bebis, G. (1999), "An ordering algorithm for pattern presentation in fuzzy ARTMAP that tends to improve generalization performance," IEEE Trans Neural Networks, vol. 10, pp. 768-778.

K. A Sumithra Devi, HOD of MCA Department is pursuing her doctoral programme at Avinashilingam University for Women. Coimbatore. She obtained her Master degree in Electronics from Bangalore university and BE in Electronics and Communication from Mysore university. Her research interests are VLSI CAD tools and partitioning techniques in VLSI technology. She has guided more than 200 undergraduate and 100 postgraduate projects. Currently she is teaching courses on operating microprocessors and advanced systems,

operating system. She has presented and published papers at international and national conferences. She is on the executive committee of many professional associations. She is a Member of CSI, ISTE, IEE and IETE.

Vijayalakshmi M.N. was born on June 11,1974, Karnataka, India, She graduated the undergraduate degree in Electronics at G.S.S.College Belgaum, India in the year 1994. She gained her MCA degree in the year 1998 at Bangalore University and has obtained her Master of philosophy degree from BharathiDasan University. She is a life member of ISTE. She has written many papers at the national and international conferences. She is pursuing her doctoral Programme at Mother Teresa Women's university, Kodaikanal. Her research interests are

Pattern recognition, data mining and neural networks.

Annamma Abraham, PhD, Addl. Asst Prof. of MCA Department, Professor of Department of MCA, has completed her Doctoral programme in Computational Fluid Dynamics from Bangalore University in 2002. She obtained his Master's Degree in Mathematics from Bangalore University. Her research interests are Instability Problems, convection in Ferro fluids and dielectric liquids. She has guided more than 100 under graduate and is currently guiding two students for their Ph. D. Currently she is teaching courses on mathematics, discrete mathematical

structures and computational techniques. She has presented and published papers at national and international conference / journals. She is a life member of ISTE and ISMFR (Indian Society for Magnetic Fluid Research).

Vasantha R, PhD, had completed her PhD in 1985, at IISc, Bangalore India. Her Thesis was entitled "Numerical Studies of Laminar Boundary Layer Flow Problems She was Gold medal contender for Ph.D. dissertation. She has written many papers at the national and international journals she Worked as a Senior Research Associate in the School of Mathematics, University of East Anglia, Norwich, England & in the Dept. of Mechanical Engineering, University of New South Wales & University of Sydney, Sydney, Australia.