# Impact of Height of Silicon Pillar on Vertical DG-MOSFET Device

K. E. Kaharudin, A. H. Hamidon, F. Salehuddin

**Abstract**—Vertical Double Gate (DG) Metal Semiconductor Field Effect Transistor (MOSFET) is believed to suppress various short channel effect problems. The gate to channel coupling in vertical DG-MOSFET are doubled, thus resulting in higher current density. By having two gates, both gates are able to control the channel from both sides and possess better electrostatic control over the channel. In order to ensure that the transistor possess a superb turn-off characteristic, the subs-threshold swing (SS) must be kept at minimum value (60-90mV/dec). By utilizing SILVACO TCAD software, an n-channel vertical DG-MOSFET was successfully designed while keeping the sub-threshold swing (SS) value as minimum as possible. From the observation made, the value of sub-threshold swing (SS) was able to be varied by adjusting the height of the silicon pillar. The minimum value of sub-threshold swing (SS) was found to be 64.7mV/dec with threshold voltage (V<sub>TH</sub>) of 0.895V. The ideal height of the vertical DG-MOSFET pillar was found to be at 0.265 µm.

Keywords-DG-MOSFET, pillar, SCE, vertical

#### I. INTRODUCTION

THE Double-gate Metal Oxide Semiconductor Field Effect transistor (MOSFET) has been actively researched especially in terms of minimizing short channel effect (SCE). One of the popular types of double-gate MOSFET is known as vertical DG-MOSFET. The basic architecture of vertical DG-MOSFET consists of a silicon ridge of few tenth of nanometer in thickness, which is regarded as the active area of the MOSFET [1]. It might be recognized as a silicon pillar separating two gates. The channel length of the vertical DG-MOSFET is normally adjusted by ion implantation and diffusion techniques. The advantage of the vertical DG-MOSFET is that the channel length is not dependent on the use of lithography. It can be easily fabricated with both back gates aligned together [2]. The main advantage of this architecture is due to its high possibility in reducing short channel effect (SCE).

Short channel effect (SCE) has become the main problem in conventional MOSFET device structure. SCE occurs when the source and drain region become too close to each other. If the effective channel length ( $L_{\rm eff}$ ) becomes too short, the depletion region from drain will reach the source region and subsequently reduces the barrier for electron injection. As consequences, leakage current ( $I_{\rm OFF}$ ) and drain induced barrier lowering (DIBL) will be increased. The way to overcome this

K. E. Kaharudin, A. H. Hamidon, and F. Salehuddin are with Faculty of Electronics and Computer Engineering, Universiti Teknikal Malaysia Melaka, Hang Tuah Jaya, Durian Tunggal, 76100 Melaka (e-mail: khairilezwan@yahoo.com.my,hamid@utem.edu.my,fauziyah@utem.edu.my).

problem is by constructing vertical pillar. As the drain region is located on the top of pillar, the effective channel length  $(L_{\text{eff}})$  will not be dependent with physical gate length  $(L_{g})$ . Hence, any reduction on physical gate length  $(L_{g})$  will not affect much on the effective channel length  $(L_{\text{eff}})$ .

Double-gate architecture was initially implemented in order to pursue the characteristic of a perfect switch. The term perfect switch refers to the transistor's ability to switch instantly from 'OFF' condition to 'ON' condition or vice versa [3]. In other words, a transistor is open, there is no current flow. And when the switch is closed, it is expected that there should be no resistance. As a transistor shrunk in size, switching will become poorer. This happens due to off current is not zero during an open switch. As a result, switching time is increased and the transistor's performance becomes poor. The way to overcome this problem is to design a gate electrode that is wrapped around several sides of the conducting channel, hence improving electrostatic control of the transistor [3].

The excellent switching speed characteristic can be obtained by controlling the subs-threshold swing (SS). Substhreshold swing (SS) occurs when  $V_{GS}$  is smaller than but close to  $V_{TH}$  [4]. At this moment, transistor is said to be in sub-threshold or weak inversion region. SS is always regarded as an important parameter which indicating the scalability limits of DG-MOSFET. It actually depict how effectively the drain current's flow could be stopped when gate-to-source current ( $V_{GS}$ ) is decreased below  $V_{TH}$ .

The good switch-off characteristic of a vertical DG-MOSFET can be realized by gate to gate capacitive coupling [5]. The voltage of both sides of the gates swing synchronously and then induces the same amount of potential charge within the channel. This will create an excellent electrostatic control of the gate over the sub-threshold leakage current. It shows how much change in the gate voltage is required to change the drain current by one decade. This response characteristic is known as sub-threshold swing and is expressed in (1) [4]:

$$SS = \left[\frac{d(\log_{10} I_{DS})}{dV_{GS}}\right]^{-1} \tag{1}$$

# II. MATERIAL AND METHODS

A. N-Channel Vertical DG-MOSFET Device Design Using SILVACO TCAD

P-type silicon with <100> orientation is used as the main substrate for this experiment. Initial silicon was then injected

by boron with concentration of 1x10<sup>15</sup> atom/cm<sup>3</sup>. The silicon was etched in order to form a pillar or a ridge that separates the two gates. The simulation process was followed by the gate oxidation process. The gate oxidation process used the dry oxidation method instead of wet oxidation because the thickness of oxidation can be better controlled through dry oxidation. The thickness of gate oxide was a very important parameter in vertical dimension that determines the gate control. The next step was to dope a substrate ion (boron) into the silicon with concentration of 9.55x10<sup>12</sup> atom/cm<sup>3</sup>. This was actually done for the purpose of threshold voltage adjustment in the Vertical DG-MOSFET.

The next simulation process was to deposit polysilicon on top of the gate oxide, and a layer of oxide was developed on top of the polysilicon deposition. The polysilicon and polysilicon oxide was etched away to form a gate polysilicon. The gate was made of polysilicon due to its ability of preventing source/drain ions to be penetrated into a channel region.

Phosphor dosage of  $1x10^{18}$  atom/cm<sup>3</sup> was then doped into polysilicon gate. This was done in order to increase the conductivity of polysilicon since polysilicon is a low conductivity metal. The conductivity of the gate would affect the switching frequency of the transistor.

In order to get an optimum performance for Vertical DG-MOSFET device, indium was doped in the substrate. After the process of halo doping, sidewall spacers were deposited. Sidewall spacers were then used as a mask for source/drain implantation. They were actually used to separate the gates with source/drain metal as to prevent them from being short-circuited since there is always process variation occurring in the fabrication process. Arsenic atom with concentration of 1.25 x 10<sup>18</sup> was implanted to ensure the smooth current flow in Vertical DG-MOSFET device.

Compensation implantation is utilized later by implanting phosphor dosage of  $2.51 \times 10^{12}$  atom/cm<sup>3</sup>. This step was taken in order to reduce parasitic effects that can lower the current. The top of the structure was then contacted with aluminum metal. The aluminum layer was deposited on the top of the structure's surface and any unwanted aluminum was etched to develop the contacts [6], [7]. Next, the metallization and etching were performed to form electrode at drain, source and gate.

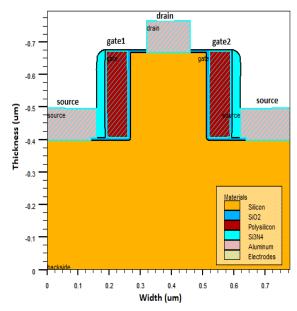

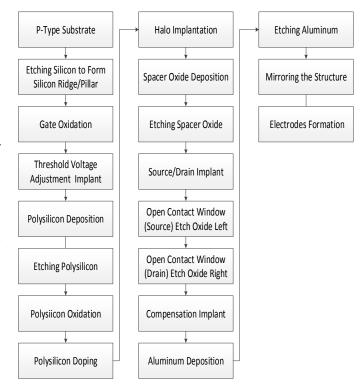

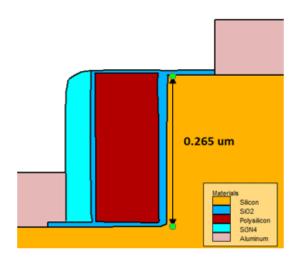

The final vertical DG-MOSFET device structure was completed by mirroring the right-hand side structure as depicted in Fig. 1. The flowchart of simulation process is illustrated in Fig. 2.

After the devices were built by utilizing **ATHENA** module, the designed device was then simulated in **ATLAS** module in order to extract electrical characteristics such as the  $I_D$  versus  $V_{GS}$  curve. The subs-threshold swing (SS) value was then extracted from that particular curve [8].

Fig. 1 Structure of Vertical DG-MOSFET device

Fig. 2 Vertical DG-MOSFET's Process Simulation Flowchart

### B. Device Simulation

Numerical simulation is a very useful method in investigating the physical nature of a vertical DG-MOSFET device [9]. By utilizing ATLAS, the electrical characteristics of a transistor can be determined precisely. Simulation results presented in this study were retrieved using SILVACO TCAD software, ATHENA and ATLAS module.

The initial point for the simulation is a structure represented

in Fig. 1. The essential input process parameters that have been used in the structure of vertical DG-MOSFET device were substrate implant dose, halo implant tilt angle, gate-oxide diffusion temperature, threshold voltage ( $V_{TH}$ ) implantation dose,  $V_{TH}$  implantation energy, halo implantation dose, halo implantation energy, source/drain (S/D) implantation dose, S/D implantation energy, compensation implantation dose and compensation implantation energy. The amount of input process parameters used in this design was summarized in Table I.

TABLE I

INPUT PROCESS PARAMETERS OF VERTICAL DG-MOSFET DEVICE

| Process Parameters             | Units                 | Level   |

|--------------------------------|-----------------------|---------|

| Gate Oxidation Temperature     | C°                    | 930     |

| V <sub>TH</sub> Implant Dose   | atom cm <sup>-3</sup> | 9.55E12 |

| V <sub>TH</sub> Implant Energy | kev                   | 10      |

| $V_{TH}$ Implant Tilt          | degree                | 7       |

| Pocket-Halo Implant Dose       | atom cm <sup>-3</sup> | 1.17E13 |

| Pocket-Halo Implant Energy     | kev                   | 170     |

| Pocket-Halo Implant Tilt       | degree                | 24      |

| S/D Implant Dose               | atom cm <sup>-3</sup> | 1.25E18 |

| S/D Implant Energy             | kev                   | 45      |

| S/D Implant Tilt               | degree                | 80      |

| Compensate Implant Dose        | atom cm <sup>-3</sup> | 2.51E12 |

| Compensate Implant Energy      | kev                   | 63      |

| Compensate Implant Tilt        | degree                | 7       |

#### III. RESULTS AND DISCUSSION

The output response's results of the experiment obtained by using ATHENA and ATLAS module were discussed. Later, the optimization in obtaining the minimum subthreshold swing (SS) value of vertical DG-MOSFET device was done using **numerical** simulation approach.

#### A. Analysis of Vertical DG-MOSFET Device

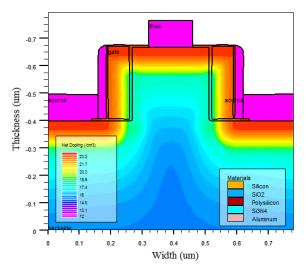

Fig. 3 shows the doping concentration across the Vertical DG-MOSFET device. The figure also shows the concentration of silicon, silicon dioxide, polysilicon, silicon nitride and aluminum. Doping concentration is one of the important factors in the fabrication process. This decides the electrical characterization of the MOSFET [10]. A good doping concentration will ensure the transistor works well with excellent gate control and fewer leakage currents.

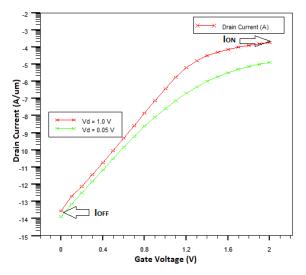

Fig. 4 shows the graph of sub-threshold drain current  $(I_d)$  versus gate voltage  $(V_G)$  at drain voltage  $V_D=0.05\ V$  and voltage  $V_D=1.0\ V$  for Vertical DG-MOSFET device. The value of the off-leakage current  $(I_{OFF})$  and drive current  $(I_{ON})$  can be extracted from the graph.

The initial threshold voltage ( $V_{TH}$ ) value of this result was at 0.892V and the SS value was at 118.2mV/dec. The initial value of sub-threshold swing (SS) was observed to be quite high. This may significantly affect the switching speed of the vertical DG-MOSFET device. In the next section, several numerical simulations were done in order to obtain the possible minimum value of sub-threshold swing (SS).

Fig. 3 Contour Mode of Vertical DG-MOSFET device

Fig. 4 Subs-Threshold  $I_D$ -V $_{GS}$  curve for Vertical DG-MOSFET device

# B. Numerical Simulation by Varying the Height of the Vertical DG-MOSFET Pillar

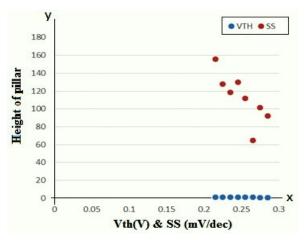

Several simulations were done in order to investigate the impact of silicon pillar's height towards the value of subthreshold swing (SS). The value of input process parameters such as gate-oxide diffusion temperature, threshold voltage ( $V_{TH}$ ) implant dose,  $V_{TH}$  implant energy, halo implant dose, halo implant energy, source/drain (S/D) implant dose and etc. were fixed as initial values. The observation was only focused on varying the structural parameter which is the height of the silicon pillar depicted in Fig. 5. Eight set of experiments were run and the results are shown in Table II. It was observed that the pillar's height variation had contributed a very random and large effect on the value of SS as illustrated in Fig. 6. However, there were no significant changes in the values of  $V_{TH}$ . They were observed to be nearly constant as depicted in

Fig. 6. The range of threshold voltage  $(V_{TH})$  values were observed to be between 0.876V and 1.101V.

Fig. 5 The height of Vertical DG-MOSFET's Pillar

It was predicted that the values of SS were being affected by other input process parameters. From Table II, it was observed that the minimum value of SS was at 64.7 mV/dec with  $V_{TH}$  value of 0.895V. Therefore, the suitable height of the **pillar** for vertical DG-MOSFET was found to be at  $0.265~\mu m$ . Any applied height higher than  $0.285~\mu m$  will damage the structure of the device. Hence, they were not suitable to be applied for the particular mesh grid definition of the device structure. The comparison value of SS with other researchers is as recorded in Table III [11], [12].

Fig. 6 X-Y Scatter graph for V<sub>TH</sub> and SS value vs Height of the Pillar

| Sample of<br>Experiment | Height of the<br>Pillar (µm) | V <sub>TH</sub> (V) | SS (mV/Dec) |

|-------------------------|------------------------------|---------------------|-------------|

| 1                       | 0.215                        | 1.011               | 155.9       |

| 2                       | 0.225                        | 0.946               | 127.6       |

| 3                       | 0.235                        | 0.892               | 118.2       |

| 4                       | 0.245                        | 1.101               | 129.6       |

| 5                       | 0.255                        | 0.966               | 111.8       |

| 6                       | 0.265                        | 0.895               | 64.7        |

| 7                       | 0.275                        | 0.876               | 101.5       |

| 8                       | 0.285                        | 0.877               | 91.9        |

TABLE III

COMPARISON RESULTS OF SUB-THRESHOLD SWING (SS) VALUE IN VERTICAL DG-MOSFET

|          | Result from this work     |             | Result from other Researcher 1 [11] | Result from other Researcher 2 [12] |

|----------|---------------------------|-------------|-------------------------------------|-------------------------------------|

| Exp. No. | Height of the Pillar (µm) | SS (mV/Dec) | SS (mV/Dec)                         | SS (mV/Dec)                         |

| 6        | 0.265                     | 64.7        | 83                                  | 70-80                               |

## IV. CONCLUSION

In conclusion, the minimum value of sub-threshold swing (SS) in the vertical DG-MOSFET device was successfully obtained and predicted using SILVACO TCAD's simulation software. There are many physical limitations involved as the pillar gets higher, exceeding the molecular or atomic limitations of the substrate and dopant. Sub-threshold swing (SS) is the main response focused in this research as it is an important factor to decide whether the MOSFET possesses an excellent switch-off characteristic or not. High sub-threshold swing (SS) is to be avoided in order to obtain a higher switching speed response on/off or logic high/low transition. Numerical simulation was utilized by ATLAS module in determining the possible minimum SS value of the vertical DG-MOSFET device. From the observation made, it can be concluded that the minimum value of SS can be retrieved by varying the height of the silicon pillar. However, the retrieved SS values are observed to be random and non-linear due to the effect of input process parameters variation in the device. The minimum value of sub-threshold swing (SS) was found to be

at 64.7 mV/dec with threshold voltage ( $V_{TH}$ ) of 0.895 V. The ideal height of vertical DG-MOSFET pillar was found to be at  $0.265 \ \mu m$ .

#### ACKNOWLEDGMENT

The authors would like to thank to the Ministry of Higher Education (MOHE) for sponsoring this work under project (PJP/2012/FKEKK(11C)/S01111) and the Faculty of Electronics and Computer Engineering (FKEKK), Universiti Teknikal Malaysia Melaka (UTeM) for the moral support throughout the project.

#### REFERENCES

- J. Moers et al., 2007, "Vertical p-Channel Double-Gate MOSFETs", *Institute of Thin Films and Interfaces (ISG), Research Center Jülich*; 52425 Jülich, Germany.

- [2] J.E. Suseno and R. Ismail., 2012, "Design of Double gate Vertical MOSFET using Silicon On Insulator (SOI) Technology", *International Journal of Nano Devices, Sensors and Systems*, Vol. 1, No. 1, May 2012, pp. 34-38.

- [3] Isabelle Ferain, Cynthia A. Colinge and Jean-Pierre Colinge., 2011, "Multigate Transistor as the Future of Classical Metal-oxide-semiconductor Field-effect Transistors", Nature, vol 479, pp. 310-316.

- [4] V. K. Yadav and A. K. Rana., 2012, "Impact of Channel Doping on DG-MOSFET Parameters in Nano Regime-Tcad Simulation", *International Journal of Computer Application*, Vol. 37 to 11, pp. 36-41.

- [5] Qiang Chen, Keith. A. Bowmen, Evans M. Harrel, and James D. Meindl, 2003, "Modeling the scaling limits of Double-gate MOSFETs with physics-Based Compact Short-Channel Models of Threshold voltage and subs-threshold swings", *IEEE Circuits and devices magazine*.

- [6] Elgomati H, Majlis BY, Ahmad I, Salehuddin F, Hamid FA, Zaharim A, Apte PR (2011) Application of taguchi method in the optimization of process variation for 32nm CMOS technology. *Australian Journal Basic Applied Science* 5(7), 346–355.

- [7] Elgomati HA, Ahmad I, Salehuddin F, Hamid FA, Zaharim A, Majlis BY, Apte PR (2011), "Optimal solution in producing 32nm CMOS technology transistor with desired leakage current". Int. J. Semiconductor Phy. Quantum. Electron. Optoelectron., 14(2): 145-151.

- [8] Goel AK, Merry M, Arkenberg K, Therkildsen E, Chiaburu E, Standfest W (1995). "Optimization of Device Performance Using Semiconductor TCAD Tools". Silvaco International, Product Description.

- [9] F. A. Rahon, M. Rahon and A. Guen Bouazza., 2013, "Study and Simulation n-MOSFET Transistor Single Gate Using SILVACO Software", International Journal of NanoScience and Nanotechnology, Vol. 4, No. 1, pp 91-103.

- [10] Fauziyah Salehuddin, Ibrahim Ahmad, Fazrena Azlee Hamid, and Azami Zaharim, u. Hashim and P.R. Apte, 2011, "Optimization of input process parameters variation on threshold voltage in 45nm NMOS device", *International Journal of the Physical Sciences* Vol. 6(30), pp. 7026 – 7034.

- [11] I. Saad, N. Bolong, P. Divya and K. T. T. Kin, 2011, "Performance Design and Simulation Analysis of Vertical Double Gate MOSFET (VDGM)", UKSim 13th International Conference on Modelling and Simulation.

- [12] M. M. A. Hakim, T. Uchino, W. R. White, P. Ashburn, L. Tan, O. Buiu and S. Hall, "Improved Sub-threshold slope in RF Vertical MOSFETS using a Frame Gate Architecture", *University of Southampton*, Southampton, SO17 1BJ, UK, Dept. of EEE, *University of Liverpool*, Brownlow Hill, Liverpool L69 3GJ, UK.