# Low Voltage Squarer Using Floating Gate MOSFETs

Rishikesh Pandey, and Maneesha Gupta

Abstract—A new low-voltage floating gate MOSFET (FGMOS) based squarer using square law characteristic of the FGMOS is proposed in this paper. The major advantages of the squarer are simplicity, rail-to-rail input dynamic range, low total harmonic distortion, and low power consumption. The proposed circuit is biased without body effect. The circuit is designed and simulated using SPICE in  $0.25\mu m$  CMOS technology. The squarer is operated at the supply voltages of  $\pm 0.75V$ . The total harmonic distortion (THD) for the input signal 0.75Vpp at 25 KHz, and maximum power consumption were found to be less than 1% and  $319\mu W$  respectively.

Keywords—Analog signal processing, floating gate MOSFETs, low-voltage, Spice, squarer.

## I. Introduction

OW power consumption increases the battery lifetime and the reliability of the portable systems. The most efficient method to reduce the power consumption is lowering the supply voltage because power is directly proportional to the square of the supply voltage. A voltage squarer is a useful non-linear building block [1]-[4] in various circuits such as multipliers, modulators, phase comparators, etc. This paper suggests a new squarer circuit based on FGMOS transistors and shows how FGMOS transistors can be used to reduce the threshold voltage requirement to get rail-to-rail input dynamic range and low power/ low voltage operation. Floating gate MOSFETs have been used to design digital-to-analog (D/A) and analog-to-digital (A/D) converter [5], voltage-controlled resistors [6]-[8], electronic programming [9], neural networks [10], operational transconductance amplifier [11], multipliers [12]-[17], attenuator [16], and squarers [15]-[17]. The squarer proposed in this paper is expected to be useful in the area of low-voltage analog signal processing applications. The analysis of the second order effects such as channel length modulation and mobility degradation show that they have little influence on the proposed circuit. The paper is organized as follows: the operation of the FGMOS is discussed in section II. In section III, the squarer using FGMOS is proposed. A detailed analysis of the channel length modulation and mobility degradation on the performance of the proposed squarer circuit is presented in section IV. In section V, SPICE simulation results are presented to verify the theoretical analysis and to demonstrate the effectiveness of the proposed circuit. The paper is concluded in Section VI.

Rishikesh Pandey is with the Division of Electronics and Communication Engineering, Netaji Subhas Institute of Technology, New Delhi-110078, India, on leave from CET, IFTM Campus, Moradabad, U.P., India, phone: +91-9811201961, fax: +91-1125099022, (e-mail: riship23@gmail.com)

Maneesha Gupta is with the Division of Electronics and Communication Engineering, Netaji Subhas Institute of Technology, New Delhi-110078, India (e-mail: maneeshapub@gmail.com)

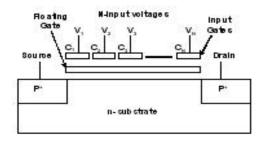

Fig. 1. Structure of an N-input FGMOS transistor

#### II. OPERATION OF FGMOS

The structure of a typical N-input FGMOS is shown in Fig. 1. The voltage on the floating gate  $(V_{FG})$  is expressed as [18]:

$$V_{FG} = \frac{\sum_{i=1}^{N} C_i V_i + C_{fd} V_{DS} + C_{fs} V_{SS} + C_{fb} V_{BS} + Q_{FG}}{C_T} \tag{1}$$

where  $C_1,C_2,C_3,\ldots,C_N$  are the input capacitances between control gate and floating gate,  $\sum_{i=1}^N C_i$  is the sum of N-input capacitances,  $C_{fd}$  is the overlap capacitances between floating-gate and drain,  $C_{fs}$  is the overlap capacitances between floating-gate and source and  $C_{fb}$  is the parasitic capacitance between floating gate and substrate,  $V_i$  is the input voltage of  $i^{th}$  input gate ,  $V_{DS}$  is the drain-to-source voltage,  $V_{SS}$  is the source voltage and  $V_{BS}$  is the substrate- to-source voltage,  $C_T$  is the total capacitance of the floating-gate and  $V_{FG}$  is the residual charge.

The total capacitance is given as:

$$C_T = \sum_{i=1}^{N} C_i + C_{fd} + C_{fs} + C_{fb}$$

(2)

The residual charge at the floating gate can be neglected using method suggested in [19]. Therefore equation (1) reduces to:

$$V_{FG} = \frac{\sum_{i=1}^{N} C_{i} V_{i} + C_{fd} V_{DS} + C_{fs} V_{SS} + C_{fb} V_{BS}}{C_{T}}$$

(3)

If

$$\sum_{i=1}^{N} C_i >> C_{fd}, C_{fs}, C_{fb}, \tag{4}$$

then equations (2) and (3) are modified as:

$$C_T = \sum_{i=1}^{N} C_i \tag{5}$$

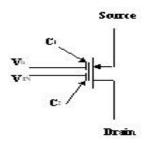

Fig. 2. Two-input FGMOS transistor

$$V_{FG} = \frac{\sum_{i=1}^{N} C_i V_i}{C_T} \tag{6}$$

The current equation for the N-input FGMOS has been obtained by modifying the conventional MOSFET equation. The current  $I_p$  in the saturation region is expressed as follows:

$$I_{p} = \frac{K_{p}}{2} \left\{ V_{DD} - \left( \frac{\sum_{i=1}^{N} C_{i} V_{i}}{C_{T}} \right) + |V_{Tp}| \right\}^{2}$$

(7)

where

$$K_p = \mu_p C_{OX} \frac{W}{L} \tag{8}$$

is the transconductance parameter,  $\mu_p$  is the mobility,  $C_{OX}$  is the gate-oxide capacitance per unit area, W/L is the aspect ratio of the transistor, and  $V_{Tp}$  is the threshold voltage of the FGMOS. In the 2-input FGMOS transistor shown in Fig. 2, voltages  $V_b$  (dc bias voltage) and  $V_{IN}$  (input voltage) are applied at the two terminals. Due to the bias voltage  $V_b$  the threshold voltage  $V_{Tp}$  adjusts itself to a new value  $V_{Tp,equ}$ :

$$V_{Tp,equ} = \frac{V_{Tp} - V_b k_{11}}{k_{12}} \tag{9}$$

where  $k_{11} = C_1/C_T$ ,  $k_{12} = C_2/C_T$  are the capacitive coupling ratio and  $C_T (= C_1 + C_2)$  is the total capacitance of the floating-gate. By choosing appropriate values of  $V_b$ ,  $k_{11}$ , and  $k_{12}$  in (9), the threshold voltage  $(V_{Tp,equ})$  of the FGMOS becomes lower than the threshold voltage  $(V_{Tp})$  of the conventional MOSFET [20].

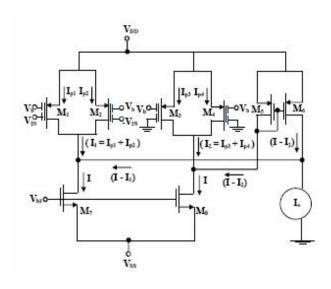

## III. FGMOS BASED SQUARER

The proposed FGMOS based squarer is shown in Fig. 3. The squaring function is being performed by  $M_1$ ,  $M_2$ ,  $M_3$ , and  $M_4$  which are 2-input FGMOS transistors, whereas  $M_5$ ,  $M_6$ ,  $M_7$ , and  $M_8$  which are used for proper biasing are MOS transistors. All these transistors are biased in the saturation region. The transistors  $M_1$ ,  $M_2$ ,  $M_3$ , and  $M_4$  are perfectly matched i.e.

$$K_{pi} = K_p, V_{Tpi} = V_{Tp}, and k_{i1} = k_{i2} = k_1$$

(10)

where i=1, 2, 3, 4. The transistors  $M_5$  and  $M_6$  form the current mirror and  $M_7$  and  $M_8$  set the bias current. From Fig. 3, it is evident that there is no body effect. The output current  $I_0$  is given as

$$I_o = I_1 - I_2 = (I_{p1} + I_{p2}) - (I_{p3} + I_{p4})$$

(11)

Fig. 3. Proposed FGMOS based squarer

where  $I_{p1}$ ,  $I_{p2}$ ,  $I_{p3}$ , and  $I_{p4}$  are the currents through  $M_1$ ,  $M_2$ ,  $M_3$ , and  $M_4$  respectively and are obtained using (7), as follows

$$I_{p1} = \frac{K_p}{2} \left\{ V_{DD} - k_1 (V_b + V_{IN}) + |V_{Tp}| \right\}^2$$

(12)

$$I_{p2} = \frac{K_p}{2} \left\{ V_{DD} - k_1 (V_b - V_{IN}) + |V_{Tp}| \right\}^2$$

(13)

$$I_{p3} = \frac{K_p}{2} \left\{ V_{DD} - k_1 V_b + |V_{Tp}| \right\}^2 \tag{14}$$

$$I_{p4} = \frac{K_p}{2} \left\{ V_{DD} - k_1 V_b + |V_{Tp}| \right\}^2 \tag{15}$$

where  $V_{IN}$  is the input voltage,  $V_b$  is the bias voltage of FGMOS, and  $V_{DD}$  is the supply voltage. Substituting equations (12)- (15) in (11), we get:

$$I_o = K_p k_1^2 V_{IN}^2 (16)$$

From equation (16), it is clear that the output current  $I_o$  is dependent upon input voltage and independent of the bias voltage  $V_b$ . The proposed squarer requires a fully differential input voltage with a proper common-mode DC voltage, which is provided by bias voltage  $V_b$ . If the capacitive coupling ratio is chosen as  $K_1 = C_1/C_T = 0.5$  and the bias voltage  $V_b$  is connected to the power supply  $V_DD$ , the squarer will be biased at half of the supply voltage. From equation (5) it is clear that the input dynamic range of the squarer has increased. It is observed from the above analysis that the bias voltage  $V_b$  in 2-input FGMOS reduces the threshold voltage as well as increases the input dynamic range.

# IV. SECOND ORDER EFFECTS

In this section the effects of channel length modulation and mobility degradation on the proposed squarer are discussed.

1) Channel Length Modulation Effect: The current  $I_p$  of 2-input FGMOS including channel length modulation effect is

$$I_{p} = \frac{K_{p}}{2} \left\{ V_{DD} - k_{1}(V_{b} + V_{IN}) + |V_{Tp}| \right\}^{2} (1 + \lambda V_{DS})$$

(17)

where  $\lambda$  is the channel length modulation parameter. Considering this effect, equations (12)- (15) are modified as

$$I_{p1} = \frac{K_p}{2} \left\{ V_{DD} - k_1 (V_b + V_{IN}) + |V_{Tp}| \right\}^2 (1 + \lambda V_{DS1})$$

(18)

$$I_{p2} = \frac{K_p}{2} \left\{ V_{DD} - k_1 (V_b - V_{IN}) + |V_{Tp}| \right\}^2 (1 + \lambda V_{DS2})$$

(19)

$$I_{p3} = \frac{K_p}{2} \left\{ V_{DD} - k_1 V_b + |V_{Tp}| \right\}^2 (1 + \lambda V_{DS3})$$

(20)

$$I_{p4} = \frac{K_p}{2} \left\{ V_{DD} - k_1 V_b + |V_{Tp}| \right\}^2 (1 + \lambda V_{DS4})$$

(21)

Substituting equations (18)-(21),  $V_{DS1} = V_{DS2}$  and  $V_{DS3} = V_{DS4}$  in equation (11), we get:

$$I_o = K_p k_1^2 V_{IN}^2 (1 + \lambda V_{DS1}) + K_p \lambda (V_{DD} - k_1 V_b + |V_{Tp}|)^2 (V_{DS1} - V_{DS3})$$

(22)

For smaller values of drain-to source voltages  $V_{DS1}$  and  $(V_{DS1}-V_{DS3})$ , the effect of channel length modulation in (22) can be neglected.

2) Mobility Degradation Effect: The current  $I_p$  of 2-input FGMOS including mobility degradation effect is

$$I_p = \frac{K_p}{2} \frac{(V_{DD} - k_1(V_b + V_{IN}) + |V_{Tp}|)^2}{(1 + \theta(V_{DD} - k_1(V_b + V_{IN}) + |V_{Tp}|))}$$

(23)

In (23),  $\theta(V_{DD} - k_1(V_b + V_{IN}) + |V_{Tp}|) << 1$ , where  $\theta$  is the mobility degradation parameter. Using Taylor's series expansion and neglecting the higher order terms, equation (23) is approximated as

$$I_p = \frac{K_p}{2} (V_{DD} - k_1 (V_b + V_{IN}) + |V_{Tp}|)^2$$

$$* (1 - \theta(V_{DD} - k_1 (V_b + V_{IN}) + |V_{Tp}|))$$

(24)

Considering this effect, equations (12)- (15) are modified as

$$I_{p1} = \frac{K_p}{2} (V_{DD} - k_1 (V_b + V_{IN}) + |V_{Tp}|)^2$$

$$* (1 - \theta(V_{DD} - k_1 (V_b + V_{IN}) + |V_{Tp}|))$$

(25)

$$I_{p2} = \frac{K_p}{2} (V_{DD} - k_1 (V_b - V_{IN}) + |V_{Tp}|)^2$$

$$* (1 - \theta(V_{DD} - k_1 (V_b - V_{IN}) + |V_{Tp}|))$$

(26)

$$I_{p3} = \frac{K_p}{2} (V_{DD} - k_1 V_b + |V_{Tp}|)^2$$

$$* (1 - \theta(V_{DD} - k_1 V_b + |V_{Tp}|))$$

(27)

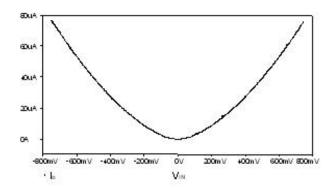

Fig. 4. I-V characteristic of the proposed squarer

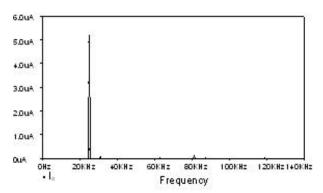

Fig. 5. Frequency spectrum of the proposed squarer for  $V_{IN} = 0.75 V_{PP}$ .

$$I_{p4} = \frac{K_p}{2} (V_{DD} - k_1 V_b + |V_{Tp}|)^2$$

$$* (1 - \theta(V_{DD} - k_1 V_b + |V_{Tp}|))$$

(28)

Substituting equations (25)-(28) in equation (11), we get

$$I_o = K_n k_1^2 V_{LN}^2 (1 - 3\theta (V_{DD} - k_1 V_b + |V_{Tn}|)) \tag{29}$$

From equation (29), we see that the term  $(V_{DD} - k_1 V_b + |V_{Tp}|) << 1$ , causes only the gain error. Since output current is the square of the input voltage, mobility degradation effect can be neglected.

## V. SIMULATION RESULTS

The proposed squarer circuit has been simulated using SPICE in  $0.25\mu m$  CMOS technology. The squarer operates at the supply voltages of  $\pm 0.75V$ . Fig. 4 shows the simulation results of the squarer. The I-V characteristic in Fig. 4 shows the squaring function behaviour for the input voltages  $(V_{IN})$  from -0.75V to 0.75V. The spectrum of the output waveform is shown in Fig. 5. From Fig. 5, it is observed that the total harmonic distortion (THD) is less than 1% for the input voltage  $V_{IN}=0.75V_{PP}$ . The simulation results are consistent with the theoretical results calculated by (16). The total power dissipation of the proposed circuit is  $319\mu\mathrm{W}$ .

## VI. CONCLUSION

In this paper a new low-voltage FGMOS based squarer has been proposed. The proposed squarer operates at the supply voltages of  $\pm 0.75V$ . It has rail-to-rail input range, low power dissipation and fairly low THD. The analysis of the channel length modulation and mobility degradation effects show that they have little influence on the proposed squarer circuit. The simulation results have been presented to demonstrate the feasibility of the proposed squarer.

Rishikesh Pandey received M.Sc. in Electronics from D.D.U. Gorakhpur University, Gorakhpur in 2000 and M. Tech. in Electronics Design and Technology in 2003 from Centre for Electronics Design and Technology of India, Gorakhpur. He was Lecturer in Electronics and Communication Engineering Department at B.I.T. Muzaffarnagar from 2003-2004, and College of Engineering and Technology, Moradabad from 2004-2007. From 2007 till date, he is working as Assistant Professor in College of Engineering and Technology, Moradabad and is presently on leave from August 2006 for doing Ph. D. from Netaji Subhas Institute of Technology, New Delhi. His teaching and research interests are in the areas of Analog and Digital Signal Processing, VLSI design, Analog and Digital Integrated Circuits, and Microprocessors.

### REFERENCES

- I. Filanovsky and H. Baltbs, "Simple CMOS analog square rooting and squaring circuits," *IEEE Trans. Circuits Systems - part I*, vol.39, no.4, pp. 312-315, 1992.

- [2] S. Liu and Y. Hwang, "CMOS squarer and four-quadrant multiplier," IEEE Trans. Circuits Systems - part I, vol.42, no.2, pp. 119-122, 1992.

- [3] G. Giustolisi, G. Palmisano, and G. Palumbo,"1.5 V power supply CMOS voltage squarer," *Electronics Letters*, vol.33, no.13, pp. 1134 - 1136, 1997.

- [4] K. Kimura,"A bipolar four-quadrant analog quarter-square multiplier consisting of unbalanced emitter-coupled pairs and expansions of its input ranges," *IEEE J. Solid-Stare Circuits*, vol.29, no.1, pp. 46-55, 1994.

- [5] Y. Liming, S.H.K. Embadi, and E. Sanchez-Sinencio," A floating gate MOSFET D/A converter," in Proc. IEEE Int. Symp. Circuits Systems, Hong Kong, 1997, pp. 409-412.

- [6] R. Pandey, and M. Gupta," A New FMOS Voltage-Controlled Resistor," in Proc. IEEE International Conference on Intelligent and Advanced Systems, ICIAS-2007, Malaysia, 2007, pp. 1392-1395.

- [7] R. Pandey, and M. Gupta,"A Novel Voltage-Controlled Grounded Resistor Using FGMOS Technique," in Proc. IEEE International Conference on Multimedia, Signal Processing and Communication Technologies IMPACT-2009, Aligarh, India 2009, pp. 16-19.

[8] M. Gupta, and R. Pandey, "FGMOS Based Low-Voltage Tunable Floating

- [8] M. Gupta, and R. Pandey, "FGMOS Based Low-Voltage Tunable Floating Resistor," *Journal of Active and Passive Electronic Devices*, to be published.

- [9] Y. Berg, and T.S. R. Lande, "Programmable floating gate MOS logic for low-power operation," in Proc. IEEE Int. Symp. Circuits Systems, ISCAS'97, Hong Kong, 1997, pp. 1792-1795.

- [10] B.W. Lee, B. J. Sheu, and H. Yang, "Analog floating gate-synapses for general purpose VLSI neural computation," *IEEE Trans. Circuits Syst.*, vol. 38, pp. 654-657, June 1991.

- [11] J. Ramirez-Angulo, S.C. Choi, and G. G. Altamirano, "Low voltage circuits building blocks using multiple input floating gate transistors," *IEEE Trans. Circuits Syst. -I*, vol. 42, no. 11, pp. 971-974, 1995.

[12] H. R. Mehrvarz, and C.Y. Kwok, "A novel multi-input floating-gate

- [12] H. R. Mehrvarz, and C.Y. Kwok, "A novel multi-input floating-gate MOS four-quadrant analog multiplier," *IEEE J. Solid-State Circuits*, vol. 31, no. 8, pp. 1123-1131, 1996.

- [13] J.F. Schoeman, and T-H. Joubert, "Four quadrant analogue CMOS multiplier using capacitively coupled dual-gate transistors," *Electron. Lett.*, vol. 32, no. 3, pp. 209-210, 1996.

- [14] J. J. Chen, S. I. Liu, and Y. S. Hwang, "Low-voltage single supply four quandrant multiplier using floating-gate MOSFETs," in Proc. IEEE Int. Symp. Circuits Systems, ISCAS'97, Hong Kong, 1997, pp. 237-240.

- [15] S. Vlassis, and S. Siskos, "Analogue squarer and multiplier based on floating-gate MOS transistors," *Electron. Lett.*, vol. 34, no. 9, pp. 825-826, 1998.

- [16] S. Vlassis, T.Th. Yiamalis, and S. Siskos, "Analogue computational circuits based on floating-gate transistors," in Proc. IEEE Int. Conf. Electr. Circuits Syst. ICECS'99, Greece, 1999, vol. I, pp. 129-133.

- [17] S. Vlassis, and S. Siskos, "Design of voltage-mode and current-mode computational circuits," *IEEE Transactions on Circuits and Systems-I*, vol. 51, no. 2, pp. 329-341, 2004.

- [18] T. Inoue, H. Nakane, Y. Fukuju, and E.S. Sinencio, "A Design of a Low-voltage Current-Mode Fully- Differential Analog CMOS Integrator Using FG-MOSFETs and Its Implementation," *Analog Integrated Circuits and Signal Processing*, vol. 32, pp. 249-256, 2002.

- and Signal Processing, vol. 32, pp. 249-256, 2002.

[19] E.R. Villegas, and H. Barnes, "Solution to trapped charge in FGMOS transistors," *Electron. Lett.*, vol. 39, no. 19, pp. 1416 1417, 2003.

- [20] S. Yan, and E. Sanchez-Sinencio, "Low Voltage Analog Circuit Design Techniques: A Tutorial," *IEICE Trans. Analog Integrated Circuits and Systems*, vol. E00-A, no. 2, pp. 1-17, 2000.

Maneesha Gupta received B.E. in Electronics and Communication Engineering from Government Engineering College, Jabalpur in 1981, M.E. in Electronics and Communication Engineering from Government Engineering College, Jabalpur in 1983 and Ph.D. in Electronics Engg. (Analysis, Synthesis and Applications of Switched Capacitor Circuits) from Indian Institute of Technology, Delhi in 1990. Dr. Gupta held the positions of Lecturer in Electronics and Communication Engineering Department at Government Engineering College, Jabalpur from 1981 to 1982, Kota Engg. College, Kota from 1986 to 1988, YMCA Institute of Engg., Faridabad in 1998 and Netaji Subhas Institute of Technology, New Delhi from 1998 to 2000. She is currently working as Assistant Professor in Electronics and Communication Engineering (ECE) Department of the Netaji Subhas Institute of Technology, New Delhi from 2000. Her teaching and research interests are Switched Capacitors Circuits and Analog Signal processing. She has co-authored over 20 research papers in the above areas in various international/national journals and conferences. She got best paper award for her paper in IETE journal of Education in 2001.