# High Speed NP-CMOS and Multi-Output Dynamic Full Adder Cells

Reza Faghih Mirzaee, Mohammad Hossein Moaiyeri, Keivan Navi

Abstract—In this paper we present two novel 1-bit full adder cells in dynamic logic style. NP-CMOS (Zipper) and Multi-Output structures are used to design the adder blocks. Characteristic of dynamic logic leads to higher speeds than the other standard static full adder cells. Using HSpice and 0.18μm CMOS technology exhibits a significant decrease in the cell delay which can result in a considerable reduction in the power-delay product (PDP). The PDP of Multi-Output design at 1.8ν power supply is around 0.15 femto joule that is 5% lower than conventional dynamic full adder cell and at least 21% lower than other static full adders.

**Keywords**—Bridge Style, Dynamic Logic, Full Adder, High Speed, Multi Output, NP-CMOS, Zipper.

#### I. INTRODUCTION

FULL Adder is the fundamental gate in many arithmetic circuits, such as adders and multipliers. Thus, enhancing the performance of the full adder block leads to the enhancement of the overall system performance [1], [2]. Therefore, many efforts have recently done to implement high-speed and low-power 1-bit full adder cells with smaller area [10]-[20].

A full adder cell is a three-input and two-output block in which the outputs are obviously the addition of three inputs. Adding two different numbers, A and B,  $a_i$  and  $b_i$  are the  $i^{th}$  digit of the numbers. Carry input bit,  $C_{in}$ , derives from the previous block. The outputs, Sum and  $C_{out}$ , are the result of the sum operation. The functionality of a 1-bit full adder cell is:

$$Sum = A \oplus B \oplus C_{in} \tag{1}$$

$$C_{\text{out}} = A.B + A.C_{\text{in}} + B.C_{\text{in}}$$

(2)

Many approaches have been presented to decrease the total number of transistors to implement a given logic function such as pseudo-NMOS, pass-transistor logic, etc. The standard CMOS logic requires 2N transistors to implement an N input logic function, while pseudo-NMOS needs N+1 transistors. It has static power consumption due to its constant switched-on pull-up network. The disadvantage of pass-

R. Faghih Mirzaee and M. H. Moaiyeri are with Science and Research Branch, Islamic Azad University, Tehran, Iran (e-mail: r.faghih@seiau.ir; Moaiyeri@seiau.ir).

K. Navi is with the Faculty of Electrical and Computer Engineering, Shahid Beheshti University, GC, Tehran, Iran (phone: +98-21-29902286; fax: +98-21-22431804; e-mail: navi@sbu.ac.ir).

transistor logic is poor voltage levels and reduced noise margins.

Dynamic is an alternative logic style to design a logic function. N+2 transistors are needed in this approach, N transistors to implement a pull-up or pull-down network and 2 transistors for the clock signal which is lower than static case. Some advantages of dynamic logic are: faster switching speeds, no static power consumption, non-ratioed logic, full swing voltage levels and less number of transistors [1].

There is not any static power consumption in dynamic circuits. It only consumes dynamic power because no static path exists between  $V_{DD}$  and GND. Higher speed is the major advantage of the dynamic logic design. Lower number of transistors per gate and absence of short circuit current are the reasons for faster switching speeds.

The main drawback is higher power dissipation than static logic due to the higher switching activity. The average power consumption in a generic CMOS gate is measured by equation (3). Although the static power consumption does not exist, the overall dissipation can be higher when compared to a static logic gate. However, with high speed operation of dynamic logic, this drawback is negligible.

$$P_{\text{avg}} = P_{\text{dynamic}} + P_{\text{short-circuit}} + P_{\text{static}}$$

(3)

In this paper we present two novel single-bit full adder cells in dynamic logic style. One of them is introduced in NP-CMOS (Zipper) logic and the other one in Multi-Output logic [3]. Both structures are optimized and tested separately in different voltages. Because of the dynamic mode, the speeds of the cells are much higher than the conventional static full adders in all voltages. A conventional dynamic and several standard static full adders are selected to be compared with:

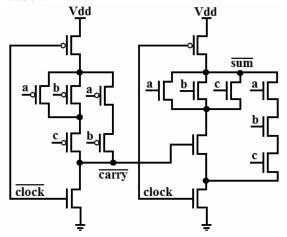

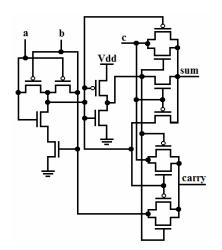

- 1) The conventional dynamic full adder cell [1]. It has 16 transistors and is based on NP-CMOS logic style (Fig. 1).

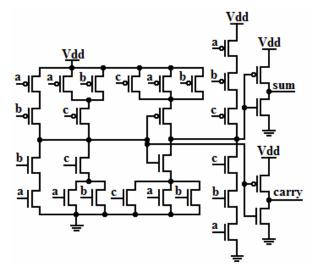

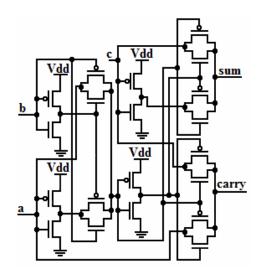

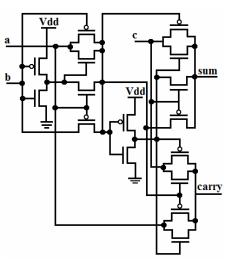

- The complementary pass-transistor logic (CPL) full adder [4], [5]. It has 32 transistors and is based on the CPL logic (Fig. 2).

- 3) The conventional CMOS full adder [5]. It has 28 transistors and is based on the regular CMOS structure (Fig. 3).

- 4) The transmission-gates CMOS (TGCMOS) full adder [6]. It has 20 transistors and is based on transmission gates (Fig. 4)

- 5) The low power implementation of the full adder cell

which has 14 transistors (14T) [7]. This cell is based on transmission gates and the low power XOR design (Fig. 5).

6) The transmission function full adder cell (TFA) [8]. It has 16 transistors and is based on the transmission function (Fig. 6).

The rest of this paper is organized as follows: In Section II, we present our new designs. Then in Section III, the simulation results are shown. Finally, Section IV contains conclusion.

Fig. 1 Conventional Dynamic Full Adder Cell

Fig. 2 CPL

Fig. 3 Conventional CMOS

Fig. 4 TGCMOS

Fig. 5 14T

Fig. 6 TFA

### II. THE PROPOSED FULL ADDER CELLS

## A. The First Design

Dynamic is an alternative logic style to design a logic function. It has some advantages in comparison with static mode such as faster switching speeds, no static power consumption, non-ratioed logic, full swing voltage levels and less number of transistors. For an N input logic function, it requires N+2 transistors versus 2N transistors in the standard CMOS logic. It only consumes the dynamic power. Finally high speed is the distinct specification of this logic style.

There are two phases in dynamic logic. For a structure where output node is connected to  $V_{\rm DD}$  by a precharge PMOS transistor, there has to be a pull-down network implemented in NMOS. When Clock=0, circuit enters the precharge phase and when Clock=1, the evaluation phase starts. All the input values should be changed at precharge phase to avoid the charge sharing problem and incorrect functionality. It is because once the output discharges at evaluation phase, there will be no path between output and  $V_{\rm DD}$  to charge it again until the next precharge phase.

The Sum output function can be described by the following equation:

$$Sum = \overline{Cout} \cdot (A + B + C_{in}) + A.B.C_{in}$$

(4)

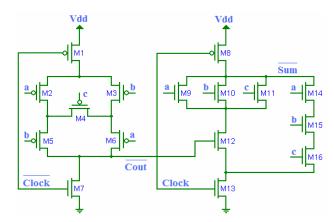

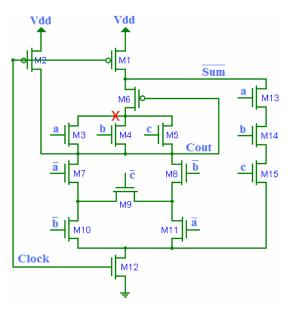

One approach is to use NP-CMOS (Zipper) logic style to implement the 1-bit full adder cell (Fig. 7). At the first stage the  $\overline{C_{out}}$  function is obtained by using the bridge style [9]. At the second stage the  $\overline{Sum}$  function is gained according to the equation (4).

The first design has 16 transistors. It has full swing voltage levels. Clock and Clock' signals cause both stages of the circuit to enter the evaluation phase simultaneously.

Fig. 7 First Proposed Full Adder Cell Using NP-CMPS Dynamic Logic

### B. The Second Design

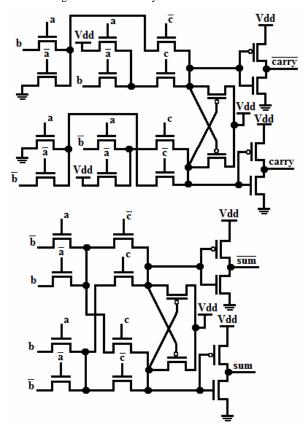

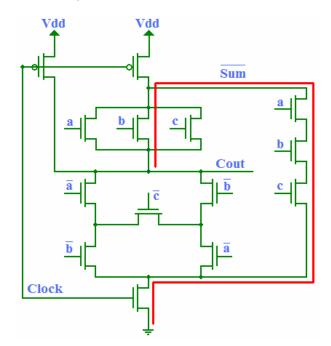

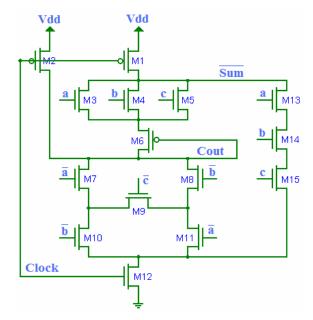

Multi-Output dynamic logic is used to design the second circuit. The second design is introduced with the aim of enhancing the first design. The primary schema for the second design is shown in Fig. 8. Two PMOS transistors are used to charge the outputs in precharge phase. The bridge style is used to obtain  $\overline{\text{Cout}}$  and then,  $\overline{\text{Cout}}$  itself creates the  $\overline{\text{Sum}}$  function. But there is a flaw which results in incorrect functionality. When the entire input signals equal to  $V_{DD}$ , minterm A.B.Cin, there is a path that connects the GND to the  $C_{\text{out}}$  output (Fig. 8). The incorrect logical value of 0 is gained instead of logical value 1 as a result.

Fig. 8 Primary Schema for the Second Design

To rectify the mentioned fault, the PMOS transistor M6 is

added to avoid the incorrect result (Fig. 9). When the input pattern is  $A=B=C_{in}=1$ , the supplemented transistor switches off and intercepts the path between GND and  $C_{out}$ . In other minterms the existence of M6 does not affect the functionality of the circuit. Thus, by adding only one transistor the functionality of the cell is corrected.

Fig. 9 Modified Schema for the Second Design

The modified second design still has some weaknesses. First, it has charge sharing problem. When the circuit enters the evaluation phase, the existent capacitor at the node X (Fig. 9) discharges the Sum output and leads to a voltage drop. The second problem occurs because of adding the PMOS transistor, i.e. the low level voltage is a little higher than 0v.

The final schema of the second design is depicted in Fig. 10. By exchanging the position of M6 with M3, M4 and M5, the charge sharing problem is eliminated considering the fact that the inputs should only be changed in precharge/predischarge phase. Therefore, we overcome the charge sharing problem without adding more transistors.

Drain and Source of M6 are connected to each other. As a result, this transistor is either off or in saturation state. Hence, when the transistor is switched on, it operates like a resistance. Equation (5) shows the proportion of the impedance of a transistor to the width and the length of the channel:

$$Z \approx L / W$$

(5)

Since L is the smallest possible technology size, enlarging the W parameter causes the equivalent impedance of M6 to decrease and the delay of the cell reduces subsequently. This also makes the low voltage level become even lower. Adding the transistors needed for the inverted inputs to the ones in the design, there will be totally 21 transistors.

Fig. 10 Final Schema for the Second Design Using Multi Output Dynamic Logic

## III. THE SIMULATION RESULTS

Both proposed designs and the other six conventional full adder cells (Conventional Dynamic, Conventional CMOS, CPL, TGCMOS, 14T and TFA) are all simulated using HSpise and 0.18µm CMOS technology at room temperature.

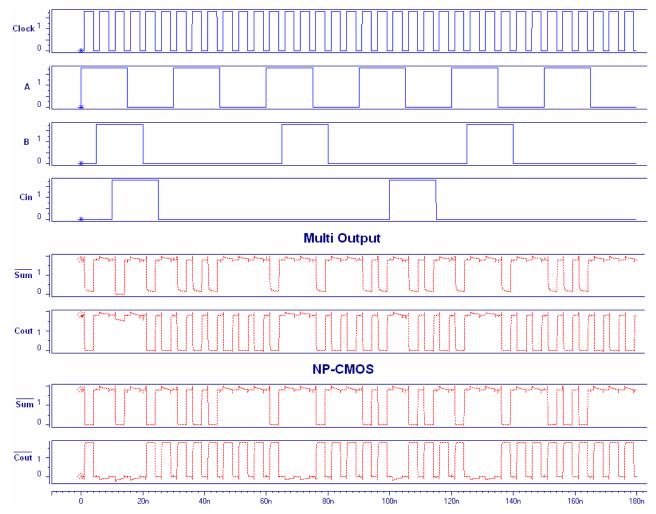

Because of dynamic logic characteristic, the inputs should be changed in precharge/predischarge phase and the results are obtained during evaluation phase. The output signals at the power supply of 1.8v are depicted in Fig. 11 for both proposed cells. The frequency of clock signal is 200MHz.

The delay parameter is calculated from the time that the clock signal reaches 50% of the supply voltage level, to the time that the output reaches the same voltage. The falling propagation delay is separately measured for every output discharge and their maximum is reported as the delay of the cell. Since there is a precharge phase for the Sum output, the rising propagation delay equals zero. The average power consumption during all the transitions is considered as the power consumption parameter. Finally the power-delay product (PDP) is the multiplication of the maximum delay and the average power consumption as shown in equation (6).

$$PDP = Max (Delay) * Avg (Power Consumption)$$

(6)

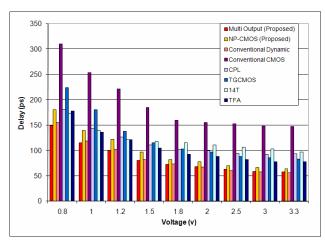

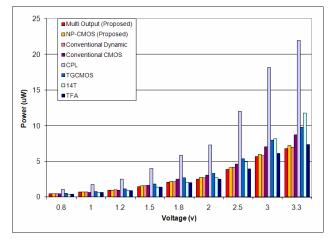

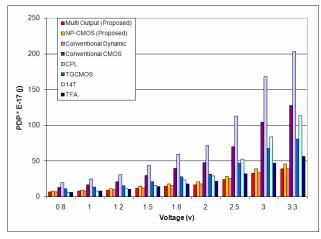

As dynamic power is proportional to  ${\rm V_{DD}}^2$ , lowering the power supply leads to less power dissipation. Hence, simulation is done for a various range of voltages from 3.3v to 0.8v. Although high power consumption can be a drawback of dynamic logic, it is still less than some other static full adder cells. The results for delay, power consumption and PDP parameters are separately illustrated in Fig. 12, Fig. 13 and Fig. 14 respectively.

Fig. 11 Input and Output Signals for Both Designs at 1.8v (Vertical Axis is Voltage & Horizontal Axis is Time)

The results are shown in Table I at 0.8v, 1.2v and 1.8v. Using 1.8v power supply, the first design is 94% faster than Conventional CMOS, 41% faster than 14T, 26% faster than TGCMOS, 25% faster than CPL and 12% faster than TFA. It consumes 166% less power than CPL, 23% less than TGCMOS and 13% less than Conventional CMOS. The PDP is 232% lower than CPL, 119% lower than Conventional CMOS, 54% lower than TGCMOS, 29% lower than 14T and 1% lower than TFA.

The results of the second design are much better than the first one so that in 1.8v power supply, it is 120% faster than Conventional CMOS, 59% faster than 14T, 42% faster than CPL and TGCMOS, 27% faster than TFA and 2% faster than Conventional Dynamic. It consumes 181% less power than CPL, 30% less than TGCMOS, 19% less than Conventional CMOS and 3% less than Conventional Dynamic. Finally its PDP is 298% lower than CPL, 163% lower than Conventional CMOS, 85% lower than TGCMOS, 55% lower than 14T, 21% lower than TFA and 5% lower than Conventional Dynamic.

Fig. 12 Delay of the Full Adder Cells, versus Supply Voltage

ISSN: 2517-9438

Vol:4, No:3, 2010

Fig. 13 Power Consumption of the Full Adder Cells, versus Supply Voltage

Fig. 14 Power-Delay Product of the Full Adder Cells, versus Supply

TABLE I THE RESULTS FOR BOTH MULTI-OUTPUT AND NP-CMOS DESIGNS AT 0.8V, 1.2V AND 1.8V

| Voltage |                | Multi Output<br>(Proposed) | NP-CMOS<br>(Proposed) | Conventional<br>Dynamic | Conventional CMOS | CPL    | TGCMOS  | 14T     | TFA     |

|---------|----------------|----------------------------|-----------------------|-------------------------|-------------------|--------|---------|---------|---------|

| 0.8v    | Delay (ps)     | 148.78                     | 179.91                | 154.79                  | 309.78            | 181.45 | 223.9   | 173.57  | 177.54  |

|         | Power (µW)     | 0.43884                    | 0.43675               | 0.44761                 | 0.41706           | 1.0798 | 0.49525 | 0.35917 | 0.36392 |

|         | PDP * E-17 (j) | 6.5291                     | 7.8576                | 6.9286                  | 12.92             | 19.593 | 11.089  | 6.2341  | 6.461   |

| 1.2v    | Delay (ps)     | 99.832                     | 121.79                | 101.92                  | 220.88            | 126.2  | 137.85  | 120.68  | 120.65  |

|         | Power (µW)     | 0.92409                    | 0.93737               | 0.97844                 | 0.94507           | 2.4773 | 1.143   | 0.92082 | 0.85146 |

|         | PDP * E-17 (j) | 9.2254                     | 11.416                | 9.9725                  | 20.874            | 31.263 | 15.756  | 11.112  | 10.273  |

| 1.8v    | Delay (ps)     | 72.12                      | 81.728                | 73.533                  | 158.96            | 102.05 | 102.59  | 114.98  | 91.932  |

|         | Power (µW)     | 2.0815                     | 2.2045                | 2.1397                  | 2.4801            | 5.8534 | 2.7036  | 2.0288  | 1.9787  |

|         | PDP * E-17 (j) | 15.012                     | 18.017                | 15.734                  | 39.425            | 59.734 | 27.736  | 23.328  | 18.191  |

# IV. CONCLUSION

NP-CMOS and Multi-Output dynamic logic style have been used to design two novel high-speed full adder cells. Using HSpice and 0.18µm CMOS technology has revealed that the Multi-Output structure has much better performance than the other conventional static and dynamic cells. However, the power consumption is a weakness of dynamic logic, but our structures consume less power than other static cells at many voltages. The PDP of the second design is 298% lower than CPL, 163% lower than Conventional CMOS, 85% lower than TGCMOS, 55% lower than 14T, 21% lower than TFA and 5% lower than Conventional Dynamic. There was incorrect functionality in the primary schema of the Multi-Output design. After making some modifications the functionality was corrected, but still there were some drawbacks such as charge sharing problem and non-full swing voltage levels. In the final design, the charge sharing problem has been eliminated and the voltage levels have considerably been enhanced. It is worth working further on dynamic logic in the future because of its several advantages.

## REFERENCES

- J. M. Rabaey, Digital Integrated Circuits, A Design Perspective, Prentice Hall, Englewood Cliffs, NJ, 1996.

- J. Uyemura,  $CMOS\,Logic\,Circuit\,Design,$  ISBN 0-7923-8452-0, Kluwer, [2] 1999

- [3] S. M. Kang and Y. Leblebici, CMOS Integrated Circuits, Analysis and Design, McGraw-Hill, 2003.

- S. Issam, A. Khater, A. Bellaouar and M. I. Elmasry, "Circuit techniques for CMOS low-power high performance multipliers," IEEE J. Solid-State Circuit, vol. 31, pp. 1535-1544, Oct. 1996.

- R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," IEEE J. Solid-State Circuits, vol. 32, pp. 1079-1090, July 1997.

- N. Weste and K. Eshragian, Principles of CMOS VLSI Design: A System Perspective, Addison-Wesley, 1993.

- E. Abu-Shama and M. Bayoumi, "A new cell for low-power adders," in Proc. Int. Midwest Symp. Circuits Syst., 1995.

- N. Zhuang and H. Wu, "A new design of the CMOS full adder," IEEE J. of Sold-State Circuits, vol. 27, pp. 840-844, May 1992.

- K. Navi, O. Kavehie, M. Ruholamini, A. Sahafi, S. Mehrabi and N. Dadkhahi, "Low-power and high-performance 1-bit CMOS full adder cell," JCP, Journal of Computers, vol. 3, pp. 48-54, Feb. 2008.

- L. Junming, S. Yan, L. Zhenghui and W. Ling, "A novel 10-transistor low-power high-speed full adder cell," IEEE 6th International Conference Solid-State and Integrated-Circuit Technology, vol. 2, pp. 1155-1158, Oct. 2001.

#### International Journal of Electrical, Electronic and Communication Sciences

ISSN: 2517-9438 Vol:4, No:3, 2010

- [11] A. M. Shams and M. A. Bayoumi, "A structured approach for designing low-power adders," Proc. 31<sup>st</sup> Asilomar Conf. Signals, Systems Computers, vol. 1, pp. 757-761, 1997.

- [12] A. M. Shams and M. A. Bayoumi, "A novel high-performance CMOS 1bit full-adder cell," *IEEE Transactions on Circuits and Systems. II*, vol 47, pp. 478-481, May 2000.

- [13] A. M. Shams, T. K. Darwish and M. A. Bayoumi, "Performance analysis of low-power 1-bit CMOS full adder cells," *IEEE Transactions on VLSI Systems*, vol. 10, pp. 20-29, Jan. 2002.

- [14] A. A. Fayed and M. A. Bayoumi, "A low power 10-transistor full adder cell for embedded architectures," *Proc. IEEE Symp. Circuits and Systems*, vol. 4, pp. 226-229, May 2001, Sydney, Australia.

- [15] J. F. Lin, Y. T. Hwang, M. H. Sheu and C. C. Ho, "A novel high-speed and energy efficient 10-transistor full adder design," *IEEE Transactions* on Circuits and Systems I: Regular Papers, vol. 54, pp. 1050-1059, May 2007.

- [16] C. H. Chang, J. Gu and M. Zhang, "A review of 0.18um full adder performances for tree structure arithmetic circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 13, pp. 686-695, Jan. 2005.

- [17] M. Sayed and W. Badawy, "Performance analysis of single-bit full adder cells using 0.18, 0.25 and 0.35um CMOS technologies," *IEEE International Symp. on Circuits and Systems*, vol. 3, pp. 559-562, Aug. 2002.

- [18] K. Navi, A. Kazeminejad and D. Etiemble, "Performance of CMOS current mode full adders," *IEEE Proc. Int'l. Symposium Multiple Valued Logic*, pp. 27-34, May 1994.

- [19] M. Haghparast and K. Navi, "A novel reversible BCD adder for nanotechnology based systems," *American Journal of Applied Sciences* 5 (3), ISSN 1546-9239, pp. 282-288, 2008.

- [20] K. Navi, O. Kavehie, M. Rouholamini, A. Sahafi and S. Mehrabi, "A novel CMOS full adder," 20<sup>th</sup> International Conference on VLSI Design held jointly with 6<sup>th</sup> International Conference on Embedded Systems (VLSID'07), pp. 303-307, Jan. 2007, Bangalore, India.