# Sensitivity of input blocking capacitor on Output voltage and current of a PV inverter employing IGBTs

Z.A. Jaffery, Vinay Kumar Chandna, and Sunil Kumar Chaudhary

Abstract—This paper present a MATLAB-SIMULINK model of a single phase 2.5 KVA, 240V RMS controlled PV VSI (Photovoltaic Voltage Source Inverter) inverter using IGBTs (Insulated Gate Bipolar Transistor). The behavior of output voltage, output current, and the total harmonic distortion (THD), with the variation in input dc blocking capacitor ( $C_{\rm dc}$ ), for linear and non-linear load has been analyzed. The values of  $C_{\rm dc}$  as suggested by the other authors in their papers are not clearly defined and it poses difficulty in selecting the proper value. As the dc power stored in  $C_{\rm dc}$ , (generally placed parallel with battery) is used as input to the VSI inverter. The simulation results shows the variation in the output voltage and current with different values of  $C_{\rm dc}$  for linear and non-linear load connected at the output side of PV VSI inverter and suggest the selection of suitable value of  $C_{\rm dc}$ .

Keywords—DC Blocking capacitor, IGBTs, PV VSI, THD.

#### I. Introduction

OLTAGE Source Inverters (VSI) are mostly used in Photovoltaic (PV) renewable energy applications and other distributed generation (DG) systems where inverter (DC to AC converter) is the back bone of power supply [1]. It must be reliable and robust, when it is used with PV generation located in remote areas. So It is necessary to verify the output voltage and current of the inverter under different loading condition, load may be linear or non linear [2]-[3]. Under this condition the switching device (IGBTs used in this inverter) goes under tremendous voltage and current stress, thus proper protection of this device is required [4], [5] and [6]. As PV inverter converts dc(obtained from a battery charged by solar array) into ac, a dc bus voltage is maintained with the help of dc filter capacitor, which is used to protect the source (PV array in this case) from the harmonics that are coming from load side to source side because of switching action [7]-[10]. Thus it is very necessary to verify the variation of dc filter capacitor on the performance of designed PV VSI inverter under various loading conditions.

## II. PROBLEM FORMATION

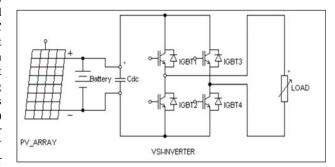

In this paper a 2.5KVA RMS controlled voltage source inverter as shown in Fig. 1. is simulated. The MATLAB-

Z. A. Jaffery, Associate Professor, Department of Electrical Engineering, Jamia Millia Islamia University, New Delhi. (e-mail: zajaffery@yahoo.com) Vinay Kumar Chandna, Assistant Professor, Department of Electrical Engineering, Jamia Millia Islamia University, New Delhi. (e-mail: vinay-chandna@yahoo.co.in)

Sunil Kumar Chaudhry, Assistant Professor, Department of Electronics Engineering, GNIT (Greater Noida Institute of Technology), MMTU University U.P. (e-mail: kumar\_csunil@yahoo.co.in)

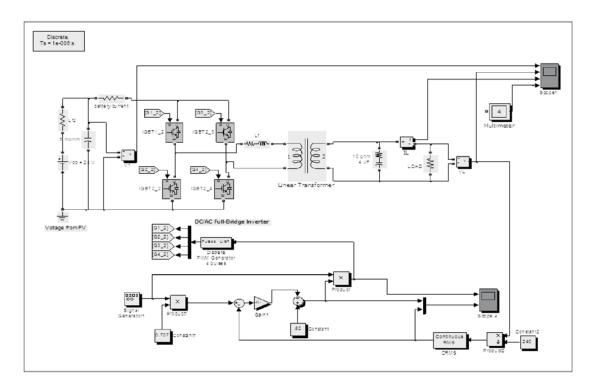

SIMULINK diagram of the inverter with a linear load connected at the output is shown in Fig. 2. The output voltage of a high-performance distributed PV system must be sinusoidal with low total harmonic distortion (THD) under both transient and periodic load disturbances. The C<sub>dc</sub> tries to maintain a constant dc voltage across input of inverter. But due to high frequency switching operation involves in the inverter operation the inverter draws a non constant current from the battery. The input blocking capacitor C<sub>dc</sub> is sensitive part of any PV inverter system [11], [12] and [13]. The variation in values of this capacitor effect the magnitude of output voltage and current and Total Harmonic Distortion (THD) present in them. In this paper variation of this important parameter (dc filter capacitor) is seen on load voltage and current for linear and non linear load. This works helps the design engineer/ Research students to select proper values of  $C_{\rm dc}$ .

Fig. 1. PV VSI inverter schematic

# III. INVERTER SIMULATION

PV voltage source inverters are described that accept do voltage (from PV array through battery) as input and produce either single-phase or three phase sinusoidal output voltage at a low frequency relative to the switching frequency. For lighting and heating loads, voltage source square wave inverter is ideally suited as the root mean square (RMS) value of the output voltage is the only requirement that have to be controlled, but for many applications perfect sine wave is required. The higher outputs are made available to different loads with the help of suitable transformers. Voltage regulation control and sine wave generation control can easily be obtained by using Pulse Width Modulation (PWM) technique, thus PWM technique is used in this paper for simulation purpose.

Fig. 2. MATLAB-SIMULINK model of PV Voltage Source Inverter with linear load signals and the carrier signal can be expressed as

The linear and non-linear load taken for the simulation purpose is analogous to 2 kW heating element. Table I shows the summary of the main parameters of proposed 2500 VA inverter and load characteristics.

TABLE I SPECIFICATION OF PROPOSED 2500VAPV-VSI

| S. No. | Parameter                           | Value with unit                                               |  |

|--------|-------------------------------------|---------------------------------------------------------------|--|

| 1      | Rated Power                         | 2500VA                                                        |  |

| 2      | Rated output frequency              | Frequency at Load $= f_{load}$ 50Hz                           |  |

| 3      | Rated output voltage                | $Vo_{load} = 240V$                                            |  |

| 4      | Battery voltage                     | $V_{\rm dc}$ =24V                                             |  |

| 5      | Battery and lead wire resistance    | $R_{\mathrm{batt}} - 30 \ \mathrm{m}\Omega$                   |  |

| 6      | Inverter switching frequency        | $f_{sw} = 12 \text{ kHz}$                                     |  |

| 7      | DC filter capacitor C <sub>dc</sub> | $4700 \mu F$                                                  |  |

| 8      | Linear load                         | $R=32.2\Omega$                                                |  |

| 9      | Non linear load                     | Diode Rectifier with RL Load $(R = 40\Omega, L = 4\text{mH})$ |  |

A suitably designed and controlled switching power converter supplies the rated voltage, current and frequency in specific range needed for load. In order to design control strategies of a switching converter, it is necessary to know the static and dynamic behavior of system, under linear and non-linear loading patterns [10]-[13]. From the PWM modulation, the analysis of harmonic components in the proposed inverter can be preformed. The output voltage produced by comparison of the two reference

$$V_0 = (\theta) = A_0 + \sum_{n=1}^{\infty} (A_n \cos n\theta + B_n \sin n\theta)$$

(1)

If there are P pulses per quarter period, and it is an odd number, then the coefficients  $B_n$  and  $A_0$  would be zero, where n is an even number. Therefore, Eq. (1) can be rewritten as

$$V_0(\theta) = \sum_{n=1,3,\dots}^{\infty} A_n \cos \theta \tag{2}$$

$$A_n = -\frac{2V_{\text{dc}}}{n\pi} \sum_{m=0}^{P} \sum_{i=1}^{P} 4[(-1)^{\text{int}(i/2)} \sin(n\alpha_{m+i})], \quad (3)$$

where m is a pulse number. The Fourier series coefficients of the conventional single-phase full-bridge inverter by sinusoidal PWM are given as

$$A_n = \frac{4V_{dc}}{n\pi} \sum_{m=1}^{P} [(-1)^m \sin(n\alpha_m)].$$

(4)

Where as % THD present in output voltage and current could be determined by the formula given below

THDin(%) =

$$\frac{\sqrt{V_{n^2} + V_{n+1^2} V_{n+2^2}}}{V_1} \times 100$$

(5)

Most of the voltage source inverter uses load voltage RMS (Root Mean Square) controller in order to regulate the amount of output voltage at load side. RMS controllers provide a cost effective, ease of implementation, solution to the voltage source inverter. A commonly used RMS voltage controller for a full-bridge inverter using MATLAB SIMULINK is shown in Fig. 2. The reference input voltage (Vref) to PWM generator block is obtained by comparing the normalized load voltage

$\begin{tabular}{ll} TABLE II \\ OUTPUT VOLTAGE AND $\%$THD FOR LINEAR LOAD \\ \end{tabular}$

S.No O/p Voltage % THD in Blocking Capacitor (µF) in Volts O/P Voltage C<sub>dc</sub> LINEAR LOAD 222.9 4.15 223 3 2 10 4.16 3 100 227.2 4.13 4 500 235.7 3 99 5 1,000 237.1 3.96 6 5,000 237.6 3.98 10,000 237.8 3.98 8 20,000 238.3 3.90 239.0 9 30,000 3.76 10 239.6 40,000 3.50 240.1 3 38 11 47 000 12 50,000 3.33 240.2 13 2.95 80.000 241.6

by an ideal and normalized value of load RMS voltage. After comparison the error signal was fed to error gain block in order to adjust value of gain according to the variation in depth of modulation due to sudden change in load. This signal is than compared with a standard modulation index (0.62) in order to get the reference signal for PWM generator ( $V_{PWM}$ ). The PWM generator than generates PWM pulses and send it to full bridge inverter block in multiplexed form for the switches present in the inverter.

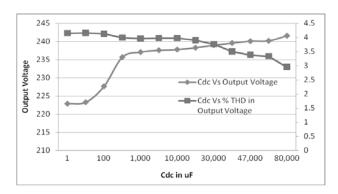

IV. SIMULATED RESULT AND CONCLUSION FOR THE EFFECT OF FILTER CAPACITOR CDC VARIATION ON OUTPUT VOLTAGE AND % THD WITH LINEAR LOAD

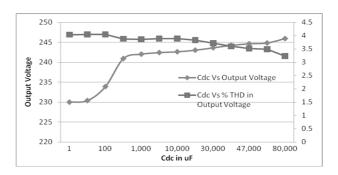

The MATLAB simulation model of RMS controlled PV VSI as shown in Fig. 2. has dc filter capacitor ( $C_{\rm dc}$ ) at the dc side of the inverter, is used to maintain the dc bus voltage. It is necessary to know the variation of this capacitor on the performance of the inverter. Table II shows the different values of the  $C_{\rm dc}$  and the corresponding values of the output voltage and percentage of total harmonic distortion (THD) for linear load and Fig. 3. shows the graphical representation of the same.

Fig. 3. Output voltage and THD variation with respect to  $C_{\rm dc}\,$

TABLE III

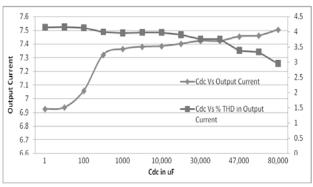

OUTPUT CURRENT AND %THD FOR LINEAR LOAD

| S.No | Blocking               | O/p Current | % THD in    |

|------|------------------------|-------------|-------------|

|      | Capacitor (µF)         | in A        | O/P Current |

|      | C <sub>dc</sub> LINEAR |             |             |

|      | LOAD                   |             |             |

| 1    | 1                      | 6.924       | 4.15        |

| 2    | 10                     | 6.936       | 4.16        |

| 3    | 100                    | 7.057       | 4.13        |

| 4    | 500                    | 7.32        | 3.99        |

| 5    | 1,000                  | 7.363       | 3.96        |

| 6    | 5,000                  | 7.38        | 3.98        |

| 7    | 10,000                 | 7.384       | 3.98        |

| 8    | 20,000                 | 7.401       | 3.90        |

| 9    | 30,000                 | 7.422       | 3.76        |

| 10   | 40,000                 | 7.422       | 3.76        |

| 11   | 47,000                 | 7.455       | 3.38        |

| 12   | 50,000                 | 7.461       | 3.33        |

| 13   | 80,000                 | 7.504       | 2.95        |

From the graph as shown in Fig. 3., the lower values of  $C_{\rm dc}$  allows more distortion to interact with the input, thus THD is high and dip in the output AC voltage. The higher values of  $C_{\rm dc}$  provides low impedance path to the distortions that are coming from the switching of inverter, thus maintains the DC voltage. Hence one should select the higher value of  $C_{\rm dc}$  for better performance of inverter to maintain DC voltage under linear load. Under this condition the snubber resistor  $R_s$  and snubber capacitor  $C_s$  are kept constant at 1e5? ohm and 130nF respectively.

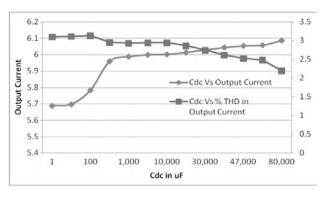

Fig. 4. Output current and THD variation with respect to  $C_{

m dc}$

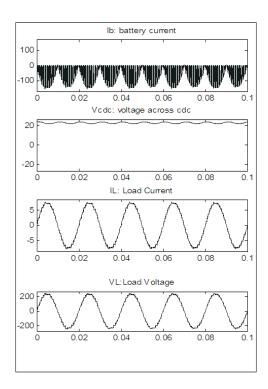

It was observed from Fig. 5.that for a value of  $47,000\mu F$  of input dc capacitor, the output voltage and current magnitude was 240V and 7.455 A, nearly equal to the rated value of designed inverter. From table II and III the THD recorded in voltage and current at this value of input capacitor was 3.38%.Fig.5. shows the variation in battery current, Voltage across  $C_{\rm dc}$ , Load current and Load voltage of PV-VSI with linear load having  $C_{\rm dc}$  value  $47,000\mu F$ .

Fig. 5. Battery current, Voltage across  $C_{

m dc}$ , Load current and Load voltage of PV-VSI with linear load

TABLE IV OUTPUT VOLTAGE AND %THD FOR NON LINEAR LOAD

| S.No | Blocking           | O/p Voltage | % THD in    |

|------|--------------------|-------------|-------------|

|      | Capacitor (μF)     | in Volts    | O/P Voltage |

|      | $C_{ m dc}$ LINEAR |             |             |

|      | LOAD               |             |             |

| 1    | 1                  | 230         | 4.04        |

| 2    | 10                 | 230.4       | 4.05        |

| 3    | 100                | 233.9       | 4.05        |

| 4    | 500                | 240.9       | 3.88        |

| 5    | 1,000              | 242.0       | 3.86        |

| 6    | 5,000              | 242.4       | 3.89        |

| 7    | 10,000             | 242.6       | 3.89        |

| 8    | 20,000             | 243.0       | 3.83        |

| 9    | 30,000             | 243.6       | 3.72        |

| 10   | 40,000             | 244.2       | 3.60        |

| 11   | 47,000             | 244.6       | 3.52        |

| 12   | 50,000             | 244.8       | 3.49        |

| 13   | 80,000             | 245.9       | 3.23        |

# V. SIMULATED RESULT AND CONCLUSION FOR THE EFFECT OF FILTER CAPACITOR CDC VARIATION ON OUTPUT VOLTAGE AND % THD WITH NON LINEAR LOAD

Table IV shows the output voltage and % THD variation for the change in  $C_{\rm dc},$  with non-linear load and Fig. 6. shows the graphical representation, that shows the increase in the output voltage and % THD after a certain value of  $C_{\rm dc},$  even if RMS controller is used to maintain the output. Table V shows the output current and % THD variation for the change in  $C_{\rm dc},$  with linear load and Fig. 7. shows the graphical representation. The simulation shows, with the increase in the value of dc

Fig. 6. Output voltage and THD variation with respect to  $C_{\rm dc}$  with non linear load

$\label{total current and with definition} TABLE~V$  OUTPUT current AND %THD FOR NON LINEAR LOAD

| S.No | Blocking           | O/p Current | % THD in    |

|------|--------------------|-------------|-------------|

|      | Capacitor (µF)     | in Volts    | O/P Current |

|      | $C_{ m dc}$ LINEAR |             |             |

|      | LOAD               |             |             |

| 1    | 1                  | 5.688       | 3.10        |

| 2    | 10                 | 5.697       | 3.11        |

| 3    | 100                | 5.783       | 3.13        |

| 4    | 500                | 5.959       | 2.95        |

| 5    | 1,000              | 5.987       | 2.93        |

| 6    | 5,000              | 5.998       | 2.94        |

| 7    | 10,000             | 6.001       | 2.94        |

| 8    | 20,000             | 6.013       | 2.86        |

| 9    | 30,000             | 6.028       | 2.74        |

| 10   | 40,000             | 6.043       | 2.61        |

| 11   | 47,000             | 6.053       | 2.52        |

| 12   | 50,000             | 6.057       | 2.48        |

| 13   | 80,000             | 6.086       | 2.19        |

filter capacitor ( $C_{\rm dc})$  the output current and percentage THD stabilizes in a favorable range.

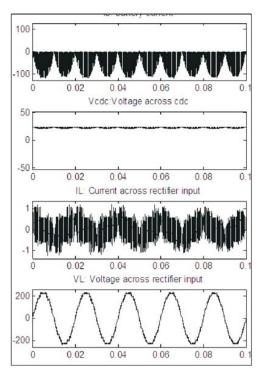

Table V shows the output current and % THD variation for the change in  $C_{\rm dc},$  with non-linear load and Fig. 7. shows the graphical representation and found that there is a non-linearity and higher % THD up to  $C_{\rm dc}$  of 100  $\mu f$  and also the effect is more for higher values  $C_{\rm dc}.$  Though the output current is stabilizing but the % THD is further increasing because of nature of load. Thus, careful selection of the filter capacitor is necessary. It was observed from Fig. 8.with a value of

Fig. 7. Output Current and THD variation with respect to C<sub>dc</sub>

47,000uF of input dc capacitor, the output voltage and current magnitude was 244.6V and 6.053 A, higher than the rated value of designed inverter. From table IV and V the THD recorded in voltage and current at this value of input capacitor was 3.52% and 2.52% respectively.

Fig. 8. Battery current, Voltage across  $C_{\rm dc},$  Load current and Load voltage of PV-VSI with non linear load

## VI. CONCLUSION

The simulation of RMS controlled PVVSI is done for various values of the filter DC capacitor ( $C_{\rm dc}$ ) for linear and non-linear load. Tables and figures show the variation in the output voltage, current and their respective percentage total harmonic distortions. The simulation results will be helpful for the practicing engineers and the students for particular selection of filter capacitor and also for the sensitivity of these parameter variations on the performance of the Photovoltaic Voltage Source inverter.

# REFERENCES

- N. Mohan, T.M. Undeland, W.P. Bobins, "Power Electronics-Convererters, Applications and Designs". 2nd edition, John Wiley & Sons, 1905

- [2] T. Philip, "Elernents of Powel. Electronics". Oxford University Press, 1998.

- [3] Sunil Kumar Chaudhry, Z.A. Jaffery, and V.K. Chandna, "Quality Assessment of Low Cost Voltage Control Voltage Source Inverter (VCVS) using Matlab Simulink". International Journal of Electrical Engineering, Vol. 3, No. 1, pp. 15–24, 2010.

- [4] Vinay Kumar Chandna, Z.A. Jaffery, and Sunil Kumar Chaudhry, "Simulation of Single Phase RMS Controlled Voltage Source Inverter (VSI) for variation in Cdc, Cs and Rs". IEEE International conference Power Electronics Drive and Energy System, PEDES 2010, 21-23 Dec., 2010.

- [5] G. Escobar, A.A. Valdez, J. Leyva-Ramos, and P. Mattavelli, "Repetitivebased controller for a UPS inverter to compensate unbalance and harmonic distortion". IEEE Trans. Ind. Electronics, Vol. 54, No. 1, pp. 504–510, Feb. 2007.

- [6] J.F. Fuller, E.F. Fuchs, and K.J. Roesler, "Influence of harmonics on power distribution system protection". IEEE Trans. Power Delivery, vol. 3, pp. 549-557, Apr. 1988.

- [7] M.E. De Oliveira Filho, J.R. Gazoli, A.J.S. Filho, and E.R. Filho, "A control method for voltage source inverter without dc link capacitor". Power electronics Specialists Conference, PESC 2008. IEEE 15-19, pp. 4432–4437, June 2008.

- [8] R. Parikh and R. Krishnan, "Modeling, simulation and analysis of an uninterruptible power supply". in Proc. 20th Int. Conf. Ind. Electron., Control Instrument., Vol. 1, pp. 485–490, Sep. 5–9, 1994.

- [9] M.K. Mishra, and K. Karthikeyan, 'Design and analysis of voltage source inverter for active compensators to compensate unbalanced and nonlinear loads". International Power Engineering Conference, 2007. IPEC 2007, pp. 649–654, 3-6 Dec. 2007.

- [10] Sangshin Kwak and H.A. Toliyat, H.A., "Parallelized Inverters Configuration with Current and Voltage Sources for High Power Applications". IEEE, 37th Power Electronics Specialists Conference, PESC '06, 2006.

- [11] N. Abdel-Rahim and J.E. Quaicoe, "Analysis and design of a multiple feedback loop control strategy for single-phase voltage-source UPS inverters". IEEE Trans. on Power Electronics, Vol. 11, No. 4, pp. 532– 541, Jul. 1996.

- [12] M.J. Ryan, W.E. Brumsickle, and R.D. Lorenz, "Control topology options for single-phase UPS inverters". IEEE Trans. Ind. Appl., Vol. 33, No. 2, pp. 493–501, Mar. 1997.

Z.A. Jaffery obtained his B. Tech and M.Tech in Electrical Engineering from Aligarh Muslim University, Aligarh, India in 1987 and 1989 respectively. He obtained his PhD degree from Jamia Millia Islamia (a central Govt. of India university) in 2004. Presently he is the associate professor in the Department of Electrical Engineering, Jamia Millia Islamia, New Delhi. His research area includes Application of soft computing Techniques in Signal Processing, Communication engineering and Computer Networking.

Vinay Kumar Chandna (M 08) graduated from Nagpur university in 1994 in electronics & power, completed his M.E. in Power System from Walchand college of Engg. Sangli, Maharashtra in the year 1997 and Ph.D. in electrical engineering, from Delhi College of Engineering, Delhi in the year 2008. His employment experience includes Walchand college of Engg., Sangli Nagpur(MAH),RKNEC Nagpur, Raj Kumar Goel institute of technology, Ghaziabad (UP), Maharaja Agarsen Institute of Technology, Delhi and presently working as Asstt. Professor in Electrical Engg. Department, Jamia Milia Islamia, New Delhi. He has more than 15 papers in International Journal/Conferences of repute. His area of interest is Application of soft computing techniques to power system, SCADA, operation, design and control, Distributed generation.

Sunil Kumar Chaudhry (M 90677291) graduated from Nagpur University in 1996 in electronics, completed his M.E. in Power Electronics from Lingaya institute of Management and Technology Faridabad, Haryana in the year 2006 and perusing Ph.D. in electrical engineering, from Jamia Milia Islamia, New Delhi. His employment experience includes Lingaya Institute of Management and Technology Faridabad, Haryana, Manav Rachna College of Engg., Faridabad, Haryana and presently working as Asstt. Professor in Electronics Engg. Department,

Greater Noida Institute of Technology (GNIT), Greater Noida, U.P His area of interest is Application of soft computing techniques to power Electronics.