ISSN: 2517-9438 Vol:3, No:1, 2009

# Packaging and Interconnection Technologies of Power Devices, Challenges and Future Trends

Raed A. Amro

Abstract—Standard packaging and interconnection technologies of power devices have difficulties meeting the increasing thermal demands of new application fields of power electronics devices. Main restrictions are the decreasing reliability of bond-wires and solder layers with increasing junction temperature. In the last few years intensive efforts have been invested in developing new packaging and interconnection solutions which may open a path to future application of power devices. In this paper, the main failure mechanisms of power devices are described and principle of new packaging and interconnection concepts and their power cycling reliability are presented.

**Keywords**—Power electronics devices, Reliability, Power Cycling, Low-temperature joining technique (LTJT)

## I. INTRODUCTION

NEW application fields of power electronics devices, like hybrid electric cars, require a maximal allowed junction temperature ( $T_{j,max}$ ) up to 175 or even 200 °C. However, and because of the decrease of power cycling reliability with increasing junction temperature, currently packaging and interconnection concepts are limiting  $T_{j,max}$  up to 150 °C.

Main weak points are the Aluminium bond wires and solder materials used for the necessary interconnection of the assembly. The concern of design engineers is increasingly focused on developing alternative joining solutions. One of these promising alternatives is the Low Temperature Joining Technique (LTJT) which has shown a surprising high power cycling reliability at high temperature swings up to 160 K ( $T_{i,max}=200^{\circ}\text{C}$ ).

# II. PRINCIPLE OF POWER CYCLING TESTS

Power cycling tests are important tool for investigation of reliability of a given packaging and interconnection concept.

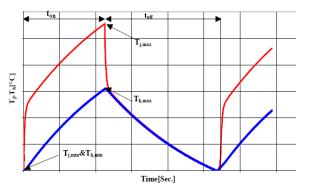

In these tests, devices are electrically stressed during the on-time  $(t_{on})$  and heated by the power dissipated by the silicon chip. Therefore, power cycling generates strong temperature gradients and inhomogeneous temperature distribution in the assembly. When the upper junction temperature  $(T_{jmax})$  is reached, DUT

Raed A. Amro is the chairman of department of computer and electrical engineering at Plaestine Polytechnic University (PPU) in Hebron/Palestine (corresponding author to provide phone: +972599098670; e-mail: raedamro@ppu.edu).

(Devices Under Test) are subsequently cooled down till the lower junction temperature  $(T_{j,min})$  is reached again (see Fig.1). The temperature swing;  $T_{jmax}$ - $T_{j,min}$  ( $\Delta T_j$ ) is a important characteristic parameter of the power cycling test and the most important factor influencing the number of cycles to failure  $(N_f)$ .

Fig. 1: Principle of power cycling test

The most observed failures occurs as result of power cycling tests are: firstly the degradation of the bonding area between the aluminium bonding wires and secondly degradation affecting the solder layers between chip and substrate and in case of power modules with base plate, solder layer between substrate and the copper base plate. The forward voltage ( $V_F$ ;  $V_{CE}$ ) and the thermal resistance between junction and a reference point ( $R_{thj-ref}$ ) of the DUT are indicators for these failures respectively. Therefore these two parameters must be observed and registered during the test. DUTs reach their end-of-life if specific limit of  $V_F$  at specific current and of  $R_{thj-ref}$  are reached. The critical increase of the forward voltage depends on the rated current of the DUT. The following general rule can be applied [1].

$$\Delta V_F[\%] = \frac{1500}{I_{rated}[A]}$$

Where  $I_{rated}$  is the rated forward current of the DUT.

The thermal resistance between junction and a reference point (mostly of the heat sink or base plate) can be calculated according to the following equation:

ISSN: 2517-9438

Vol:3, No:1, 2009

$$R_{thj-ref} = \frac{T_j - T_{ref}}{P_{diss}} \qquad [K/W]$$

Where:

$R_{thj}$ : Junction temperature

$T_{ref}$ : Temperature of the reference point

$P_{diss}$ : Dissipated power due to electrical stress

#### III. MAIN FAILURE MECHANISMS OF POWER ELECTRONICS

### A. Bond Wires Lift-Off

Bond wires used in power electronics devices have a thickness of up to 750 µm and are made of pure aluminum hardened by adding of alloying elements like silicon and nickel for corrosion control. They are used to interconnect the power silicon chip to the substrate, pins and other chips.

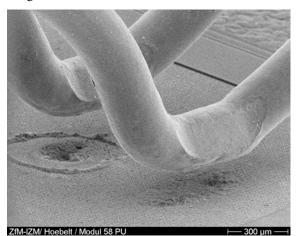

Due to the large mismatch in the thermal expansion coefficient (CTE) of the silicon (3·10<sup>-6</sup> /K) and Aluminium (22·10<sup>-6</sup> /K), chip-bond wire connection zone is exposed to strong theromechanical stress during the field aplication where the power devices are habitually heated up and cooled down. This stress leads finally to bond wire lift-off and to the completely failure of the dvice. Fig.2 shows a lifted-off bond wire as of an IGBT (Insulated Gate Bipolar Transistor) as result of power cycling the device during reliability investigation test.

Fig. 2: Lifted-off bond wires of an IGBT during power cycling

Bond wire lift-off is a self accelerating effect. Meanly, when wire lift-off occurs, the current density in the surviving wires increased significantly leading finally to their melting.

Disconnection of bond wires due to lift-off was considered as the most important reliability weak point of power electronics devices. Therefore, efforts of reliability engineer were focused on understanding and analysing of this failure mechanism employing accelerated lifetime tests (power and thermal cycling tests) and currant failure analysis. These investigations were focused in finding the optimal wire dimensional parameter, chemical composition, and electrical stress profile. A clear improvements in the reliability of the

bonding technology could be achieved in the last decade[2].

## B. Degradation of Solder Layers

In power electronics devices, soft solders are used to bond the silicon chip to the substrate and substrate to the base plate. The used solders are usually lead-based alloys like SnPb37Ag2 with melting temperature of 178 °C. However manufacturers of electronic devices are rapidly converting to lead-free materials to meet new environmental requirements. The lead-free solders are usually Tin/Silver (Sn/Ag) or variations on Sn/Ag alloys. The most used lead-free solder is the Sn96,5Ag3,5 with melting point of 221°C.

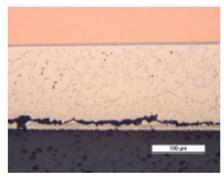

The bond between the soldered partners is mainly provided by the formation of one or more intermetallic phases and as a result of thermal stress in the application field, the different intermetallic phases coarsen rapidly and fatigue cracks initiate at the border of the solder joints where shear stress reaches its maximum and propagate within the brittle copper intermetallic phase [3]. Fig.3 shows a crack in the solder layer as result of thermal cycling of power electronics module.

Fig. 3: Crack in solder layer [4]

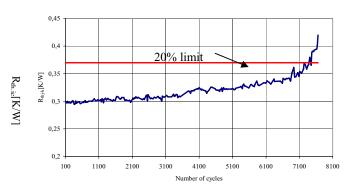

Degradations in solder layers deteriorate the dissipation of the generated heat in the chip which leads to increase in the thermal resistance of the device. Atypical behaviour of the thermal resistance of power electronics module during power cycling test is shown in Fig.4

Fig. 4: Behaviour of thermal resistance (R<sub>thic</sub>) of power module during power cycling test

ISSN: 2517-9438 Vol:3, No:1, 2009

#### IV. LOW TEMPERATURE JOINING TECHNIQUE (LTJT)

Power cycling tests at high temperature swings have shown that soft solders are the main reliability concern of power electronics devices and seem to be unable to open a path for high temperature applications.

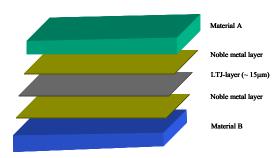

A promising alternative for soldering is the low temperature joining technique (LTJT). The technique is based on sintering of sub-micro silver flakes at temperatures above 220°C and a pressure of about 40 MPa during one minute in air. The surfaces of the parts to be joined have to obtain an oxide-free metal finish such as gold or silver [5]. The layering sequence of LTJT process is shown in Fig.5.

Fig. 5: Layering sequence of LTJ process

## Power Cycling Reliability of LTJT

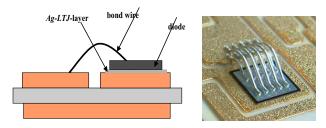

Two power cycling tests at  $\Delta T_j$ =130K ( $T_{j,max}$ =170 °C) and  $\Delta T_j$ =160K ( $T_{j,max}$ =200 °C) have been performed with test diodes based on LTJT and integrated in *easy1* package of INFINEON [6]. The bottom side connection (cathode to substrate) was realized with LTJT and improved bond wire technology was used for the top side connection (cathode to substrate). A schematic and photo of the assemblies are shown in Fig.6.

Fig. 6: One-sided LTJT devices : Schematic (left) and internal layout (right)

Considering the number of cycles at which the first failure occurred, one-sided LTJT devices show at  $\Delta T_j$ =130K power cycling reliability approx. four times higher than state-of-the-art of soldered standard modules Application of LTJT combined with improved bonding process yields to significant increase of the power cycling reliability. Even after approx. 20000 power cycles at  $\Delta T_j$ =170K ( $T_{i,max}$ =200°C) either

destructive bond wire aging nor critical increase of the thermal resistance could be observed. Power cycling lifetime of one-sided LTJT at  $\Delta T_j$ =200K lies ten times higher than being expected from state-of-the-art of power modules.

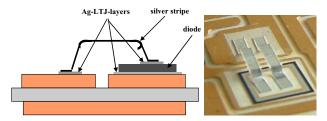

A further test at  $\Delta Tj=130~K~(T_{j,max}=200^{\circ}C)$  has performed with test diodes where bond wires are replaced by silver stripes joined to the chip using LTJT and similar to the devices in the previous test, LTJT was used to realize the bottom side connection of the chip. Fig.7 illustrates the packaging concept of these test devices.

Fig. 7: Double-sided LTJT devices : Schematic (left) and internal layout (right)

The test was stopped after 66750 power cycles without reaching the end- of- life of the devices under test. However, a slight increase of the thermal resistance of a single device could be observed. Investigations of this device by ultrasound imaging have confirmed that aging of the substrate was the reason for this increase.

# V. CONCLUSION

Important improvements in wire bonding and solder technologies could be achieved in the last years reflecting into increased power cycling capability of state-of-the-art of power devices compared to that expected from standard modules before ten years. However, standard soft solders are still reliability risk and there are experimental evidences that this technique will not be able to be reliable solution for the future applications of power devices.

Low Temperature Joining Technique (LTJT) promises to be suitable for future module set-up. Already the replacement of only chip-to-substrate solder joint (one-sided LTJT) yields significant power cycling capability. The lifetime of the one-sided LTJT devices was limited by bond wire lift-off. Taking advantages of the full performances of LTJT would however be achieved by the extension of its application for top side contacts where bond wires are replaced by silver stripes (double-sided LTJT).

## REFERENCES

- M. HELD; P. JACOB; G. NICOLETTI; P. SCACCO; M.H. POECH: Fast Power Cycling Test for IGBT Modules in Traction Application. Proc. Power Conversion and Drive Systems 1997, pp.425-430.

- AUERBACH; SCHWARZBAUER; LAMMERS; LENNIGER: Zuverlässigkeit von Al-Dickdraht-Bondverbindungen. ISHM Konferenz, München 1996.

- M. RODRIGUES; N. SHAMMAS; N. PLUMPTON; D. NEWCOMBE;

D. CREES: Static and Dynamic Finite Element Modelling of Thermal

#### International Journal of Electrical, Electronic and Communication Sciences

ISSN: 2517-9438 Vol:3, No:1, 2009

- Fatigue Effects in IGBT Modules. Microelectronics Reliability 40(2000), pp. 455-463. B. Smith, "An approach to graphs of linear forms (Unpublished work style)," unpublished.

- [4] M.-H. POECH: Schädigungsmechanismen in Lötverbindungen bei erhöhter Temperatur. VTE 14 (2002), Heft1, S. 12-18.

- [5] H. SCHWARZBAUER; R. KUHNERT: Novel Large Area Joining Technique for Improved Power Device Performance. IEEE Transactions on Industry Applications, Vol.27, pp. 93-95, 1991.

- [6] C. PANZER, T. PASSE, T. STOLZE, Z. LIANG: Clamping Technique improves IGBT Installation. PET magazine, Oct. Issue 56(2002).

Raed A. Amro was born in Dura-Hebron/Palestine on 04.03.1969. He got his high diploma in electrical engineering from university of Saarland in Germany in 1999. From 2000 to 2003 he worked as lecturers at Palestine Polytechnic University (PPU) in Hebron/Palestine. From 2003 to 2006 he was employed as scientific employee at the chair of Power Electronics and Electromagnetic Compatibility (PE/EMC) at Chemnitz university of technology/Germany, where he was involved in the research project 'New Packaging and Interconnection Technologies of Power Electronics Devices. In 2006 he got his PhD from Chemnitz university of technology with the dissertation title "Power Cycling Capability of Advanced Packaging and Interconnection Technologies at High Temperature Swings".

He is currently the **Chairman** of Department of Electrical and Computer Engineering at Palestine Polytechnic University (PPU) in Hebron-Palestine. He is also involved in teaching and developing of subjects related to industrial automation and supervising of graduation projects in the field of industrial electronics and logic control.

Dr. Amro has several publications in English and German in the field of reliability of power devices. For example:

- Evaluation of DCB based, Transfer molded Components with High Temperature Swings. 25<sup>th</sup> International PCIM conference 2004. Nuremberg/Germany (Main author).

- 2) Power Cycling with High Temperature Swing of Discrete Components Based on Different Technologies. 35th IEEE annual Power Electronics Specialists Conference PESC. Aachen/Germany (Main author)

- 3) Double-Sided Low-Temperature Joining Technique for Power Cycling Capability at High Temperature. 11<sup>th</sup> European Conference on Power Electronics and Applications, EPE2005. Dresden/Germany (Main author)

- Power Cycling at High Temperature Swings of Modules with Low Temperature Joining Technique. 18<sup>th</sup> International Symposium on Power Semiconductor Devices and ICs. ISPSD 2006. Naples/Italy (Main author)

- 5) Power cycling induced failure mechanisms in the viewpoint of rough temperature environment. 6<sup>th</sup> International Conference on Integration of Power Electronics Systems 2008. Nuremberg/Germany (co-author)