# Analysis of Bit Error Rate Improvement in MFSK Communication Link

O. P. Sharma, V. Janyani and S. Sancheti

Abstract—Data rate, tolerable bit error rate or frame error rate and range & coverage are the key performance requirement of a communication link. In this paper performance of MFSK link is analyzed in terms of bit error rate, number of errors and total number of data processed. In the communication link model proposed, which is implemented using MATLAB block set, an improvement in BER is observed. Different parameters which effects and enables to keep BER low in M-ary communication system are also identified.

**Keywords**—Additive White Gaussian Noise (AWGN), Bit Error Rate (BER), Frequency Shift Keying (FSK), Orthogonal Signaling.

#### I. INTRODUCTION

In any communication system the performance requirement are data rate, tolerable bit error rate (BER) or frame error rate (FER) and range & coverage [1]. To meet out the requirements the design constraints are power limitation, bandwidth limitation, implementation complexity (increase in complexity leads to increase in cost) and processing delay [2]. Binary data transmission is a special case of *M*-ary data transmission

MFSK communication system operates in environment where large bandwidths are available but signal power is limited. Such power limited systems rely on power efficient modulation scheme to achieve acceptable bit error and data rates. In general data rate can be improved by increasing the number of symbols at the transmitter. If this is to be done without degrading probability of error  $P_e$  then the enlarged alphabet of symbols must remain at least as widely spaced in the constellation as the original symbol set. This can be achieved without increasing transmitted power by adding orthogonal axes to the constellation space a technique which results in multidimensional signaling [3-4]. Power can also be conserved by carefully optimizing the arrangements of points in the constellation space.

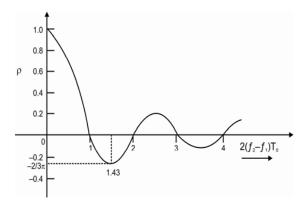

The MFSK (for M=2) symbol correlation  $\rho$  and the difference in the number of carrier half cycles contained in the symbols is shown in fig. 1. The zero crossing points

represents orthogonal signaling system and  $2(f_2-f_1)T_0=1.43$ represent a signaling system somewhere between orthogonal and antipodal. This is the optimum operating point for Binary Frequency shift Keying (BFSK) in terms of power efficiency and yields 0.8dB Carrier-to-noise ratio (CNR) saving over orthogonal BFSK. It corresponds to symbols which contain a difference of approximately 3/4 of a carrier cycle. The zero crossing point on the  $\rho$ - $T_0$  (fig.1) corresponds to orthogonal BFSK, but it is not possible to use the first zero i.e.  $2(f_2$  $f_1$ ) $T_0$ =1, if detection is incoherent. If BFSK is operated at this point the two symbols are different by only ½ a carrier cycle. A difference so small can be detected as a change in phase of 180 degree over the symbol duration but difficult to be measured reliably in this time as a change in frequency [4-5]. The minimum frequency separation for successful incoherent detection of orthogonal BFSK is therefore given by the second zero crossing point i.e.  $2(f_2-f_1)T_0=2$ , which corresponds to one carrier cycle difference between the two symbols. Similar concept is to be maintained for the MFSK for M>2.

The increased data rate realized by MFSK signaling is achieved entirely at the expense of increased bandwidth, since symbol conveys  $H=log_2M$  bits of information. The nominal spectral efficiency of orthogonal MFSK is given by

$$\eta_s = \log_2 M / (n/2)(M-1) + 2$$

(1)

where  $\eta_s$  is in bits/s/Hz; n is the selected zero crossing point on the  $\rho$ - $T_0$  (fig.1) and the signal bandwidth is defined by the first spectral nulls above and below the highest and lowest frequency symbols respectively [1, 6-8].

Fig. 1 Symbol correlation  $\rho$  and number of carrier half cycles with in the symbols

O. P. Sharma, is PhD Research Scholar, Department of Electronics and Communication Engineering at Malaviya National Institute of Technology, Jaipur, Rajasthan, India 302017 (M-098293-64944, fax: 0141-2770790; e-mail: ops\_mnit@ yahoo.co.in).

V. Janyani, Reader, Department of Electronics and Communication Engineering at Malaviya National Institute of Technology, Jaipur, Rajasthan, India 302017 (e-mail: vijayjanyani@ gmail.com).

S. Sancheti, Director, National Institute of Technology Karnataka, Surathkal, India (e-mail: sandeepsancheti@rediffmail.com).

For incoherent detection (n>=2), for n=2 the maximum spectral efficiency is given by

$$\eta_s = \log_2 M / (M+1) \tag{2}$$

In this paper improvement in BER is obtained in the communication link model proposed. It also helps to analyze / identify different parameters of communication link, which affects the BER in an M-ary system.

This paper has four sections. Brief introduction of MFSK communication is discussed in section I. Section II deals with different building blocks of MFSK communication link. Assumptions made for simulation and result analysis is in section III. Conclusion is given in section IV.

## II. COMMUNICATION LINK MODEL

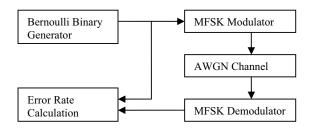

MFSK Communication link model is implemented using different MATLAB blockset as shown in fig. 2,

Fig. 2 Communication link model

Descriptions of the blocks are as follows; Bernoulli binary generator, this block generates random binary numbers, zero with probability p and one with probability 1-p. The Bernoulli distribution has mean value 1-p and variance p(1-p). The Probability of a zero parameter specifies p, and can be any real number between zero and one [1, 8-10]. MFSK Modulator Baseband block; this block modulates using the Mary frequency shift keying method. Here M, is the number of frequencies in the modulated signal. The Frequency separation parameter is the distance, in Hz, between successive frequencies of the modulated signal. If the Phase continuity parameter is set to continuous, then the modulated signal maintains its phase even when it changes its frequency. If the Phase continuity parameter is set to discontinuous, then the modulated signal comprises portions of M sinusoids of different frequencies; thus, a change in the input value might cause a change in the phase of the modulated signal. Additive White Gaussian Noise channel block; this block adds white Gaussian noise to the signal that passes through it. The relative power of noise in an AWGN channel is typically described by quantities such as Signal-to-noise ratio (SNR) per sample, Ratio of bit energy to noise power spectral density (Eb/No) or Ratio of symbol energy to noise power spectral density (Es/No) [8-10,13]. MFSK Demodulator; this block demodulates a signal that is modulated using the M-ary frequency shift keying method. Error Rate Calculation block;

this block compares input data from a transmitter with input data from a receiver. It calculates the error rate as a running statistic, by dividing the total number of unequal pairs of data elements by the total number of input data elements from one source [8-12,14]. This block produces a vector of length three, whose entries correspond to: the error rate, total number of errors, i.e. comparisons between unequal elements and total number of comparisons that the block made.

#### III. SIMULATION AND RESULT ANALYSIS

Simulation is carried out by varying different parameters in various blocks of the communication link model. Simulation is done in two parts A and B. For both parts common assumptions made are: receiver delay=1; computation delay=0; computation mode=entire frame.

Part A: - Variation of Parameter of Bernoulli binary generator block

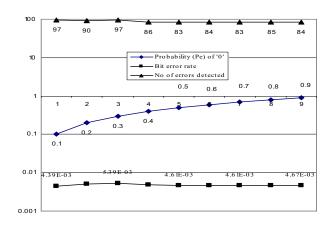

i). By varying the parameter, probability *Pe* of '0' in Bernoulli binary generator, simulation is carried out for evaluating the BER and number of errors detected. Total number of bits processed is 18000 (kept constant). The results are shown in fig. 3. Simulated values are in table I.

TABLE I

BIT ERROR RATE, NUMBER OF ERRORS DETECTED FOR DIFFERENT VALUES

OF PROBABILITY OF '0'

| Probability (Pe) of |                | Number of errors |  |

|---------------------|----------------|------------------|--|

| '0'                 | Bit error rate | detected         |  |

| 0.1                 | 0.004389       | 97               |  |

| 0.2                 | 0.005          | 90               |  |

| 0.3                 | 0.005389       | 97               |  |

| 0.4                 | 0.004778       | 86               |  |

| 0.5                 | 0.004611       | 83               |  |

| 0.6                 | 0.004667       | 84               |  |

| 0.7                 | 0.004611       | 83               |  |

| 0.8                 | 0.004722       | 85               |  |

| 0.9                 | 0.004667       | 84               |  |

Fig. 3 Probability (Pe) of '0' Vs BER and Number of errors

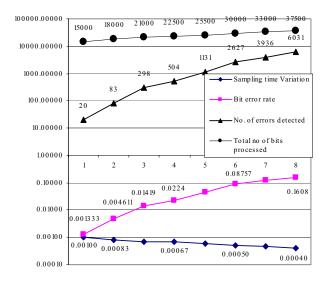

ii). By varying the sampling time parameter in Bernoulli binary generator, simulation is carried out for evaluating the BER, number of errors detected and total number of bits processed. The plot of simulated output is shown in fig. 4. simulated values obtained are in table II.

TABLE II

BIT ERROR RATE, NUMBER OF ERRORS DETECTED AND TOTAL NUMBER OF BITS

PROCESSED FOR DIFFERENT VALUES OF SAMPLING TIME

| Sampling time<br>Variation | Bit error rate | Number of<br>errors<br>detected | Total number of bits processed |

|----------------------------|----------------|---------------------------------|--------------------------------|

| 0.00100                    | 0.001333       | 20                              | 15000                          |

| 0.00083                    | 0.004611       | 83                              | 18000                          |

| 0.00071                    | 0.01419        | 298                             | 21000                          |

| 0.00067                    | 0.0224         | 504                             | 22500                          |

| 0.00059                    | 0.04435        | 1131                            | 25500                          |

| 0.00050                    | 0.08757        | 2627                            | 30000                          |

| 0.00045                    | 0.1193         | 3936                            | 33000                          |

| 0.00040                    | 0.1608         | 6031                            | 37500                          |

Fig. 4 Sampling time variation Vs BER, Number of errors detected, Total number of bits processed

Part B: - Variation of Parameter of MFSK modulator and demodulator block

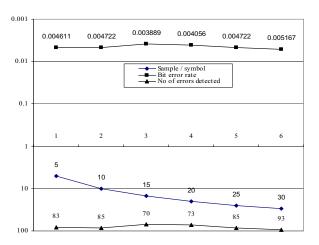

- i). By varying the parameter, sample per symbol of MFSK modulator and demodulator blocks, simulation is carried out for evaluating the BER and number of errors detected. Total number of bits processed is kept constant at 18000. As shown in fig. 5. Simulated values are in table III.

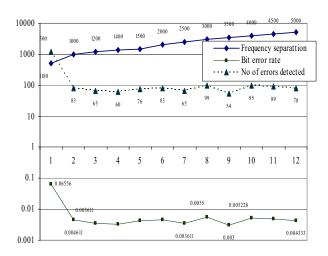

- ii). By varying the parameter, frequency separation of MFSK modulator and demodulator blocks, simulation is carried out for evaluating the BER and number of errors detected. Total number of bits processed is kept constant at 18000. As shown in fig. 6. Simulated values obtained are in table IV.

Table III Bit error rate and Number of errors detected for different values of sample/symbol

| Sample /<br>symbol | Bit error rate | Number of errors detected |

|--------------------|----------------|---------------------------|

| 5                  | 0.004611       | 83                        |

| 10                 | 0.004722       | 85                        |

| 15                 | 0.003889       | 70                        |

| 20                 | 0.004056       | 73                        |

| 25                 | 0.004722       | 85                        |

| 30                 | 0.005167       | 93                        |

Fig. 5 Bit error rate and Number of errors detected for different values of sample/symbol

TABLE IV

BIT ERROR RATE AND NUMBER OF ERRORS DETECTED FOR DIFFERENT VALUES

OF FREQUENCY SEPARATION

| Frequency separation | Bit error rate | Number of errors<br>detected |

|----------------------|----------------|------------------------------|

| 500                  | 0.06556        | 1180                         |

| 1000                 | 0.004611       | 83                           |

| 1200                 | 0.003611       | 65                           |

| 1400                 | 0.003333       | 60                           |

| 1500                 | 0.004222       | 76                           |

| 2000                 | 0.004611       | 83                           |

| 2500                 | 0.003611       | 65                           |

| 3000                 | 0.0055         | 99                           |

| 3500                 | 0.003          | 54                           |

| 4000                 | 0.005228       | 95                           |

| 4500                 | 0.004944       | 89                           |

| 5000                 | 0.004333       | 78                           |

### Result Analysis

When probability Pe of '0' is varied from 0.1 to 0.3 the BER increases rapidly. For Pe value from 0.4 to 0.9 the BER variation is nearly similar (difference of 0.0001) as shown in fig. 3. Further it can be observed from fig. 4 that, if Pe is varied from 0.1 to 0.3 there is random variation of number of errors. For Pe value 0.4 to 0.9 the value of number of errors is in between 86 to 84. When the sampling time is low, BER is

low and number of errors is less 20, for total number of bit processed to be 15000. With the increase in sampling time the BER and number of errors detected increases abruptly, as shown in fig. 4. From the simulated results obtained the optimum suggestion for BER value 0.004611, is total number of bit processed to be 18000, number of error detected is 83 and sampling time variation to be 0.00083.

As seen from fig. 5, BER increases from 0.004611 to 0.004722 when sample/symbol is increased from 5-10 samples/symbol. BER reduces to minimum value 0.003889 for 15 samples/symbol. For values 20, 25 and 30 sample/symbol simulated BER values are 0.004056, 0.004722 and 0.005167 respectively i.e. an increase in BER. Similar nature of plot is obtained for sample/symbol and number of errors detected when values of sample/symbol is varied from 5 to 30 samples per second as shown in fig. 5.

Fig. 6 Bit error rate and Number of errors detected for different frequency separation (Hz).

It can be seen from fig. 6, that an increase in frequency separation from 500Hz to 1000Hz there is drastic improvement in BER. For increase in frequency separation from 1000Hz to 5000Hz a small variation of BER in between 0.0055 to 0.003 is observed. Similarly, it can be observed from fig. 6, an increase in frequency separation from 500Hz to 1000Hz, number of errors detected drops from 1180 to 83. For further increase in value of frequency separation from 1000Hz to 5000Hz, the value of number of errors detected lies in between the maximum and minimum value of 99 and 54 respectively. Frequency separation of 3500Hz can be a good option if lower BER and low number of errors detection is considered but a greater bandwidth is needed. Depending upon the application and available bandwidth the frequency separation between symbols can be from 1000Hz to 5000Hz. The optimum suggestion from the result obtained for better BER is 15 samples/symbol and a frequency separation of 3500Hz, keeping in view that the bandwidth is not a constraint.

#### IV. CONCLUSION

MFSK communication system operates in an environment where large bandwidths are available but signal power is limited. Such power limited systems rely on power efficient modulation scheme to achieve acceptable bit error and data rates. Performance of a communication link depends upon probability  $P_e$ , which is occurrence of 0 in Bernoulli binary generator. A low value of  $P_e$  degrade the performance, also a low value of sampling time in Bernoulli binary generator may lead to high BER and number of errors are also large. If number of samples/symbol in MFSK modulator is more, than the value of BER increases on the other hand if frequency separation parameter in MFSK modulator is increased a drastic improvement in BER and number of error is observed. For improved performance i.e. low BER and number of errors the acceptable value of  $P_e$  and sampling time in Bernoulli binary generator may be 0.5 and 0.00083 sec. Further improvement in performance can be achieved, if 15 samples/symbol and frequency separation parameter 3500 in MFSK modulator is chosen. Proper selection of values of parameters in different subsection such as source, channel, modulation and demodulation may help to design and implement an efficient communication system.

#### ACKNOWLEDGMENT

Author is thankful to the technical support provided by Electronics and Communication Engineering Department, MNIT, Jaipur, Rajasthan (India).

# REFERENCES

- M. C. Jeruchin, P. Balaban, K. S. Shanmugan, Simulation of communication systems, Plenum press, New York, 1992.

- [2] S. Chen, "Adaptive minimum bit-error-rate filtering", IEE Proc.-Vis. Image Signal Process., Vol. 151, No. 1, pp. 76-85, February 2004.

- [3] Stelios A. Mitilineos, Pantelis K. Varlamos, and Christos N. Capsalis, "A Simulation Method for Bit-error-Rate- Performance Estimation for Arbitrary Angle of arrival Channel Models", *IEEE Antennas and Propagation Magazine*, Vol. 46, No. 2, pp.158-163, April 2004.

- [4] J. G. Proakis, *Digital Communications*, 4th ed., New York, McGraw-Hill 2001.

- [5] O. P. Sharma and S. Sancheti, "Performance analysis of Gray coded M-PSK", 22<sup>nd</sup> National Convention of Electronics and Telecommunication Engineers and National Seminar on Advances in Electronics and Telecommunication Technologies Vision-2020, Souvenir Technical session V, Sr. No. 09, August 04-05, 2006.

- [6] Jack H. Winters, and Jack Salz, "Upper Bounds on the Bit-Error Rate of Optimum Combining in Wireless Systems", *IEEE Trans. On Comm.*, Vol. 46, No. 12, pp. 1619-1623, December 1998.

- [7] Thomas Zwick, Christian Fischer and Werner Wiesbeck, "A Stochastic Multipath Channel Model Including Path Directions for Indoor Environments", *IEEE Journal on Selected Area in Comm.*, Vol. 20, No. 6, 0733-716/02\$17.00 © 2002 IEEE, pp. 1178-1192, Aug. 2002.

- [8] M. K. Simon and Alouini, Digital Communication over Fading Channels, Wiley-Interscience, New York, 2000.

- [9] S. Hinedi, M. Simon and D. Raphaeli, "The performance of noncoherent orthogonal M-FSK in the presence of timing and frequency errors", *IEEE Trans. Commun.*, pp. 922-33, February-April 1995

- [10] E. Grayver and B. Daneshrad, "A low power all-digital FSK receiver for deep space application", *IEEE Trans. Commun.*, PP. 911-21, May 2001.

- [11] M. Patzold, Mobile Fading Channel, Wiley, New York, 2002.

- [12] S. Chen, B. Mulgrew and L. Hanzo, "Least bit error rate adaptive nonlinear equalizers for binary signaling", *IEE Proc. Commu.*, Vol. 150, No. 1, pp. 29-36, February 2003.

#### International Journal of Electrical, Electronic and Communication Sciences

ISSN: 2517-9438 Vol:2, No:9, 2008

- [13] Chen, L. Hanzo, N.N. Ahmad and A. Wolfgang, "Adaptive Minimum Bit Error Rate Beam forming Assisted QPSK Receiver", IEEE Communications Society, pp.3389-3393, 0-7803-8533-0/04/\$20.00 (c) 2004.

- [14] O.P. Sharma, V. Janyani, S. Sancheti and S. Bhardwaj, "Channel Modeling and Security Issues for Wireless Healthcare System", VOYAGER, The Journal of Computer Science and Information Technology, ISSN 0973-4872 Vol.5, No.1 Jan-June, 2007, pp. 37-41.

Om Prakash Sharma born at Kota, Rajasthan (India) in Year 1972. He received B.E. degree in Electronics and Telecommunication from North Maharastra University, Jalgaon, India in 1996 and M.E. in Digital Communication from Jai Narayan Vyas University, Jodhpur, India, in 2001. Presently he is pursuing PhD on Channel Modeling and Detection of Signal on Fading Channels from Malaviya National Institute of Technology (Deemed University), Jaipur, India.

Mr. Sharma is life member of the Institution of Electronics and Telecommunication Engineers (IETE), India.

**Dr. Vijay Janyani** received the B.E. degree in Electronics and Communication Engineering and the M.E. degree in Electronics and Electrical Communication, both from Malaviya National Institute of Technology (MNIT) Jaipur (then known as Malaviya Regional Engineering College), Rajasthan, India in 1994 and 1996 respectively. He joined as a Lecturer at the Department of Electronics and Communication Engineering at MNIT Jaipur in 1995, where he is currently working as a Senior Lecturer. From 2002 to 2005.

he worked at the University of Nottingham, UK towards his PhD Degree in Electronics Engineering under the Commonwealth Scholarship and Fellowship Plan (UK), on the problem of time-domain modelling of nonlinear and dispersive opto-electronic materials and devices.

Dr. Janyani is a Member of the Institute of Electrical and Electronics Engineers (IEEE), Institution of Electronics and Telecommunication Engineers (IETE), Indian Society for Technical Education (ISTE) and a Fellow of Optical Society of India (OSI).

**Dr. Sandeep Sancheti** holds a PhD from the Queens University of Belfast, U.K. He obtained his B.Tech degree from Regional Engineering College, Warangal and Post graduation from Delhi College of Engineering in 1982 and 1985, respectively. Currently he is serving as a Director, National Institute of Technology Karnataka, Surathkal. His major area of research interest is High Frequency Electronics, R.F. Circuits and Systems, Microwave Antennas and Semiconductor Device Modelling. He has to his credit more than 55 research papers in national and international journals and conferences.

Dr. Sancheti is a Life fellow of Institution of Electronics & Telecommunication Engineers (FIETE), Life member of ISTE (LMISTE), Life Fellow of Broadcast Engineering Society (LFBES) and Member of Institute of Electrical and Electronics Engineers (MIEEE), USA. He has served in the capacities of Honorary Secretary and Chairman, IETE, Rajasthan Centre. He is also on the panel of number of Governing Boards and Committees at National and State level.