# A Power-Gating Scheme to Reduce Leakage Power for P-type Adiabatic Logic Circuits

Hong Li, Linfeng Li, and Jianping Hu

Abstract—With rapid technology scaling, the proportion of the static power consumption catches up with dynamic power consumption gradually. To decrease leakage consumption is becoming more and more important in low-power design. This paper presents a power-gating scheme for P-DTGAL (p-type dual transmission gate adiabatic logic) circuits to reduce leakage power dissipations under deep submicron process. The energy dissipations of P-DTGAL circuits with power-gating scheme are investigated in different processes, frequencies and active ratios. BSIM4 model is adopted to reflect the characteristics of the leakage currents. HSPICE simulations show that the leakage loss is greatly reduced by using the P-DTGAL with power-gating techniques.

*Keywords*—Leakage reduction, low power, deep submicron CMOS circuits, P-type adiabatic circuits.

### I. INTRODUCTION

BEFORE the CMOS process is scaled into deep sub-micro process, dynamic energy loss has always dominated power consumption, while leakage dissipation is little. The aggressive scaling of device dimensions and threshold voltage has significantly increased leakage current exponentially, thus the MOS devices will no longer be totally turned-off anymore. The power dissipation caused by leakage current can't be neglected anymore, which attracts extensive attentions [1]–[5].

There are several sources of leakage currents: sub-threshold leakage current due to very low threshold voltage ( $V_T$ ), gate leakage current due to very thin gate oxide ( $T_{OX}$ ), and band-to-band tunneling leakage current due to heavily-doped halo [1]–[3]. Several leakage reduction techniques, such as dual threshold CMOS, power gating technique, stacking transistor techniques, variable threshold CMOS, and input vector control have been proposed in recent years and achieved considerable energy savings [1]–[5].

Adiabatic logic is an attractive low-power approach by utilizing AC voltage supplies (power-clocks) to recycle the energy of circuits instead of being dissipated as heat. Several

Hong Li is with Faculty of Information Science and Technology, Ningbo University, Ningbo City, Zhejiang 315211, China. He is now an associate professor (e-mail: lihong2@nbu.edu.cn).

Linfeng Li is with Faculty of Information Science and Technology, Ningbo University, Ningbo City, Zhejiang 315211, China (e-mail: nbulilf@yahoo.com.cn).

Jianping Hu is with Faculty of Information Science and Technology, Ningbo University, Ningbo City, Zhejiang 315211, China. He is now a professor in Faculty of Information Science & Technology at Ningbo University (corresponding author: 86-574-87665739; fax: 86-574-87600940; e-mail: nbhjp@yahoo.com.cn).

adiabatic logic families and their applications have been reported and achieved considerable energy savings [6], [7]. Similar to power-gating techniques of conventional CMOS circuits, power-gating schemes for adiabatic circuits have been also introduced to reduce dynamic energy dissipations during idle periods [8], [9].

Base on the pact that PMOS transistors have an order of magnitude smaller gate leakage than NMOS ones, P-type CMOS design technology has been proposed to reduce the leakage power [10]. However, the previously reported P-type CMOS design technology is only investigated for conventional CMOS circuits. To the best of our knowledge, no previous investigates for leakage reductions of P-type adiabatic circuits with the power-gating approaches are presented.

This paper focuses on leakage reduction of adiabatic circuits using P-type power-gating schemes in scaled CMOS processes. A P-type power-gating scheme for P-DTGAL (P-type dual transmission gate adiabatic logic) circuits is proposed. Further, the leakage reductions of P-DTGAL circuits with the proposed P-type power-gating scheme are investigated. Taken as an example, power dissipations of an 8-bit full adder based on P-DTGAL circuits with the proposed P-type power-gating scheme are investigated in different processes, frequencies and active ratios. BSIM4 model [11] is adopted to reflect the characteristics of the leakage currents. HSPICE simulations show that the 8-bit adiabatic full adder with the P-type power-gating scheme shows significant improvement in terms of leakage power consumptions in deep sub-micron process.

### II. REVIEW OF DUAL TRANSMISSION GATE ADIABATIC LOGIC

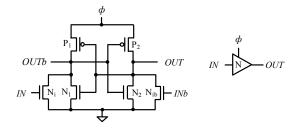

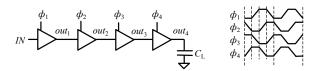

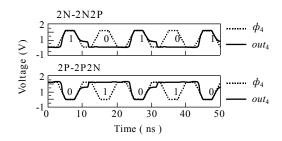

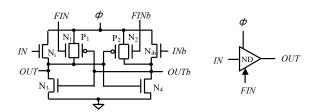

The typical adiabatic circuit 2N-2N2P is showed in Fig. 1(a) [12]. 2P-2P2N is a complementary logic, and its structure and operation are complementary to the 2N-2N2P, as shown in Fig. 1(b) [7]. Cascaded 2N-2N2P and 2P-2P2N gates are driven by the four-phase power clocks, as shown in Fig. 1(c). Their simulated waveforms are shown Fig. 1(d). It can be seen that they have non-adiabatic energy loss on output nodes, which is dependent on the load capacitance. Therefore, if they are used for driving large load capacitance, non-adiabatic energy loss is large. For quasi-adiabatic circuits such as ECRL (Efficient Charge Recovery Logic) and PAL-2N (Pass-transistor adiabatic logic with NMOS pull-down configuration) etc, the same conclusion can be obtained [6], [13].

(a) 2N-2N2P and symbol

(b) 2P-2P2N and symbol

(c) Buffer chain and power clock

(d) Simulated waveforms

Fig. 1 2N-2N2P and 2P-2P-2N buffers

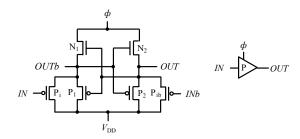

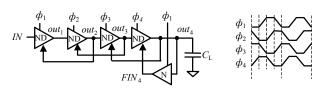

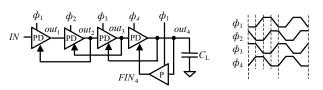

To overcome this disadvantage, a N-type dual transmission gate adiabatic logic (N-DTGAL) was presented in [14], as shown in Fig. 2. The power-clock  $\phi$  charges the output (OUT or OUTb) through  $N_i$  and  $P_1$  (or  $N_{ib}$  and  $P_2$ ) by control of the inputs (IN and INB). The energy of output nodes is recovered to  $\phi$  through  $N_1$  and  $P_1$  (or  $N_2$  and  $P_2$ ) by control of the feedback signals (FIN and FINb), which are from the outputs of the next-stage buffer. For the final-stage N-DTGAL gate in a pipelined chain, an additional 2N-2N2P buffer is used and its outputs ( $FIN_4$  and  $FINb_4$ ) control energy-recovery of the final-stage N-DTGAL gate.

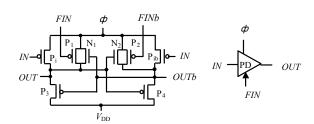

A P-type DTGAL has also been reported in [7], as shown in Fig. 3. Its structure, operation, and signal waveforms are complementary to the N-type DTGAL. For the final-stage

P-DTGAL gate in a pipelined chain, an additional 2P-2P2N buffer is used and its outputs (FIN<sub>4</sub> and FINb<sub>4</sub>) control energy-recovery of the final-stage P-DTGAL gate. Cascaded P-DTGAL and N-DTGAL gates are driven by the same four-phase power-clocks as the 2N-2N2P.

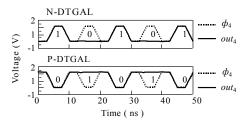

The simulated waveforms for the P-DTGAL and N-DTGAL circuits are shown Fig. 4. It can be seen that N-DTGAL and P-DTGAL haven't non-adiabatic loss on output loads. Although the additional 2N-2N2P (or 2P-2P-2N) buffer has the non-adiabatic energy loss  $CV_{TP}^2$  (or  $CV_{TN}^2$ ), this energy loss is small, because the capacitance C, which mainly consists of gate capacitance of input transistors in the N-DTGAL and P-DTGAL buffers, is far smaller than the load capacitance  $(C_L)$  of the logic circuits [7], [14].

(a) Schematic and symbol

(b) Buffer chain and power clock

Fig. 2 N-type DTGAL buffer

(a) Schematic and symbol

(b) Buffer chain and power clock

Fig. 3 P-type DTGAL buffer

Fig. 4 Simulated waveforms for N-DTGAL and P-DTGAL buffers

## III. POWER-GATING SCHEME FOR P-TYPE DUAL TRANSMISSION GATE ADIABATIC LOGIC CIRCUITS

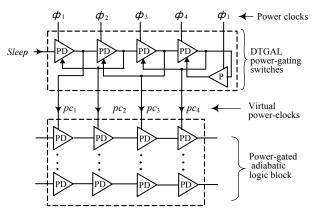

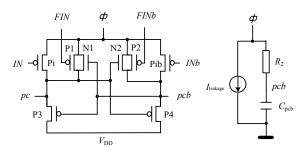

The proposed power-gating scheme for P-DTGAL circuits is shown in Fig. 5. The power-gating switches using a P-DTGAL buffer chain with large device sizes are inserted between power-clocks ( $\phi_1 - \phi_4$ ) and virtual power-clocks ( $pc_1 - pc_4$ ). They are used to disconnect the P-type adiabatic logic block from the power-clocks during idle periods.

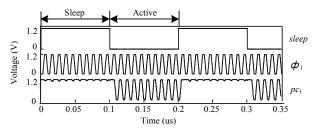

The simulated waveforms for the power-gating adiabatic circuits are shown in Fig. 6. The power-gated adiabatic circuits work in two modes under the control of *Sleep* (sleep enable signal). In sleep mode, *Sleep* is high, thus virtual power-clocks  $(pc_1 - pc_4)$  are set as high level, so that the power-gated adiabatic logic block is shut down to reduce its energy dissipation. In active mode, *Sleep* is low, thus virtual power-clocks  $(pc_1 - pc_4)$  follow power-clocks  $(pc_1 - pc_4)$ , and the power-gated adiabatic logic block works as usual.

Fig. 5 Power-gating scheme for PDTGAL circuits

Fig. 6 Simulation waveforms of power-gating adiabatic circuits

### IV. ENERGY DISSIPATIONS OF POWER-GATING SWITCHES

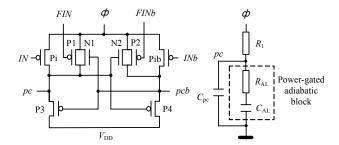

The power-gating switches introduce an additional energy loss, which can be analyzed by using the equivalent circuit of the power-gating switch shown in Fig. 7.

(a) Equivalent circuit of power-gating switch in active mode

(b) Equivalent circuit of power-gating switch in sleep mode

Fig. 7 Equivalent circuits of the power-gating switch

In active mode, the power-gated logic block can be modeled by a capacitor  $C_{\rm AL}$  and a resistor  $R_{\rm AL}$  [15]. The transmission-gate TG1 (Pi, N1, and P1) is on, and  $R_1$  is its turn-on resistance, which is in inverse proportion to the channel width of TG1.  $C_{\rm pc}$  is capacitance of the node pc, and it includes wire capacitance and the input capacitance of the next-stage P-type power-gating switch, which is proportional to the channel width of TG1. The transmission-gate TG2 (Pib, N2, and P2) is off. The energy loss per cycle in active mode introduced by the power-gating switch can be written as

$$E_{\text{active}} = \left(\frac{2R_1C_{\text{AL}}}{T/4}\right)C_{\text{AL}}V_{\text{DD}}^2 + \left(\frac{2R_1C_{\text{pc}}}{T/4}\right)C_{\text{PC}}V_{\text{DD}}^2, \quad (1)$$

where T and  $V_{\rm DD}$  are period and peak-to-peak voltage of power clocks. The first term is energy loss for supplying the power-gating adiabatic logic block, and the second term is energy loss for driving the next-stage and previous-stage P-DTGAL power-gating switches.

In sleep mode, TG1 is off, and  $I_{leakage}$  is its leakage current. TG2 is on, and  $R_2$  is its turn-on resistance, which is in inverse proportion to the channel width of TG2. The energy loss per cycle in sleep mode introduced by the power-gating switch can be written as:

$$E_{\text{sleep}} = I_{\text{leakage}} T + \left(\frac{2R_2C_{\text{pcb}}}{T/4}\right) C_{\text{pcb}} V_{\text{DD}}^2$$

(2)

The first term proportional to the channel width of TG1 is leakage energy loss of TG1. The second term is energy loss for charging and discharging node *pcb*.

Total average energy loss per cycle is written as:

$$E_{\text{AV}} = \frac{(E_{\text{active}})(T_{\text{active}}) + E_{\text{sleep}}(T_{\text{sleep}})}{(T_{\text{active}} + T_{\text{sleep}})} = (E_{\text{active}})\alpha + E_{\text{sleep}}(1 - \alpha)$$

(3)

where  $T_{\text{active}}$  is active time,  $T_{\text{sleep}}$  is sleep time, and  $\alpha = T_{\text{active}} / (T_{\text{active}} + T_{\text{sleep}})$  is active ratio.

### V. OPTIMIZATION FOR ENERGY DISSIPATIONS OF POWER-GATING SWITCHES IN DIFFERENT CMOS PROCESSES

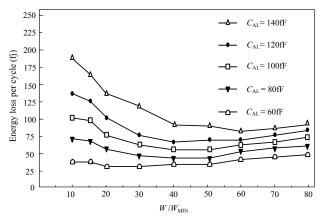

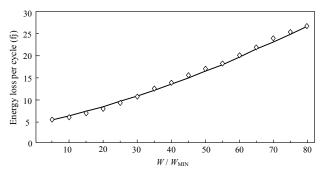

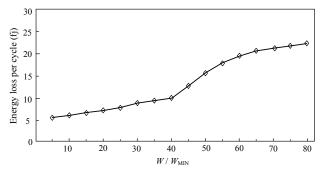

According to (1),  $E_{\text{active}}$  can be reduced by increasing channel width of TG1, because turn-on resistance  $R_1$  of TG1 is reduced. However, for a large channel width of TG1,  $E_{\text{active}}$  will be increased since  $C_{\text{PC}}$  is proportional to the channel width of TG1. Therefore,  $E_{\text{active}}$  can be minimized by choosing optimal sizes of TG1. Fig. 8 and Fig. 9 show the energy dissipation ( $E_{\text{active}}$ ) of the power-gating switch for various channel widths of TG1 in 0.09um and 0.045um process, respectively.

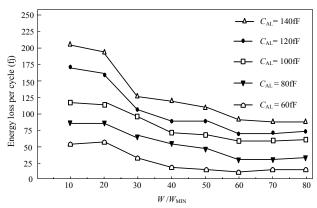

According to (2),  $E_{\rm sleep}$  can be reduced by reducing  $R_2$  and  $C_{\rm pcb}$ , which are in inverse proportion to and proportional to the channel width of TG2, respectively. Fig. 10 and Fig. 11 show the energy dissipation ( $E_{\rm sleep}$ ) per cycle of the power-gating switch for various channel widths of TG1 in 0.09um and 0.045um processes, respectively. In this simulations, the device size of the transistors (Pib, and P2) have been taken as an optimal size with  $W/L = 12\lambda/2\lambda$ , and the transistor N2 is also taken as  $W/L = 12\lambda/2\lambda$ . For 0.09um and 0.045um processes,  $\lambda$ =0.09µm and 0.026µm, respectively.

Fig. 8 Energy dissipation ( $E_{\rm active}$ ) of the power-gating switch in active mode versus channel width of the transistors (Ni and N1) in 90nm process. W is channel width of transistors (Ni and N1), and  $W_{\rm MIN}$  = 0.135 $\mu$ m. The channel width of the transistor P1 are two times as large as Ni and N1. f is 200MHz and  $V_{\rm DD}$  is 1.2V

Fig. 9 Energy dissipation ( $E_{\rm active}$ ) of the power-gating switch in active mode versus channel width of the transistors (Ni and N1)in 45nm process. W is channel width of transistors (Ni and N1), and  $W_{\rm MIN}$  = 0.069 $\mu$ m. The channel width of the transistor P1 are two times as large as Ni and N1. f is 400MHz and  $V_{\rm DD}$  is 1.0V

Fig. 10 Energy dissipation ( $E_{\rm sleep}$ ) of the power-gating switch in sleep mode versus channel width of the transistors (Ni and N1) in 90nm process. W is channel width of transistors (Ni and N1), and  $W_{\rm MIN}$  = 0.135 $\mu$ m. The channel width of the transistor P1 are two times as large as Ni and N1. f is 200MHz and  $V_{\rm DD}$  is 1.2V

Fig. 11 Energy dissipation ( $E_{\rm sleep}$ ) of the power-gating switch in sleep mode versus channel width of the transistors (Ni and N1) in 45nm process. W is channel width of transistors (Ni and N1), and  $W_{\rm MIN}$  = 0.069 $\mu$ m. The channel width of the transistor P1 are two times as large as Ni and N1. f is 400MHz and  $V_{\rm DD}$  is 1.0V

The total energy overhead of the power-gating switches can be minimized by choosing optimal sizes of TG1 according (1) to (3) for a given process, active ratio, and the power-gated adiabatic block.

### VI. LEAKAGE REDUCTION OF 8-BIT FULL ADDER BASED ON P-DTGAL CIRCUITS USING POWER-GATING SCHEME

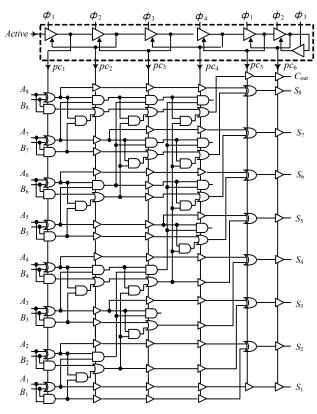

We use an 8-bit carry-lookahead adder (CLA) to show the leakage reduction of P-DTGAL power-gating circuits in deep submicron process, which is shown in Fig. 12. The power-gating switches with six-stage P-DTGAL buffer chain are inserted between power-clocks ( $\phi_1 - \phi_4$ ) and virtual power-clocks ( $pc_1 - pc_6$ ) to maintain proper pipelining operation. The phase of virtual power-clocks ( $pc_5$  and  $pc_6$ ) is the same as  $\phi_1$  and  $\phi_2$ , respectively.

Fig. 12 8-bit full adder based on P-DTGAL circuits using power-gating technique

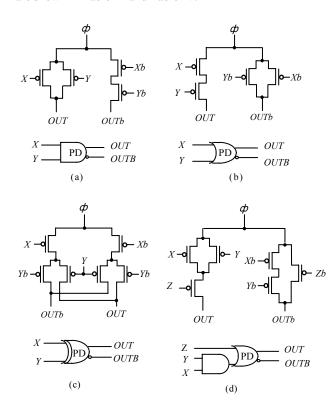

The logic gates used in the adder are realized with P-DTGAL circuits by using the PMOS pass-transistor logic block to replace the transistors ( $P_i$  and  $P_{ib}$ ) of Fig. 3(a), as shown in Fig. 13. In Fig. 13, only the P-logic input blocks are shown and the other transistors are omitted for simplicity.

In order to extract the equivalent capacitor  $C_{\rm AL}$  of the 8-bit adder based on P-DTGAL circuits for each power-clock, the simulation tests have been performed. The optimizations for the power-gating switches have also been carried out according to (3) with a given active ratio (a = 0.2).

Considering the energy overhead of the power-gating switches and acceptable area penalty. For the 90nm process, the channel width of the transistors (Pi and P1) of all P-DTGAL power-gating switches are taken with  $40W_{\rm MIN}(5.4\mu{\rm m})$ , and the channel width of the transistors (N2, Pib and P2) is taken an

optimal size with  $W/L = 12\lambda/2\lambda$  and  $\lambda=0.045\mu m$ . For the 45nm process, the channel width of the transistors (Pi and P1) of all P-DTGAL power-gating switches are taken with  $60W_{\rm MIN}$  (4.14 $\mu$ m), and the channel width of the transistors (N2, Pib and P2) is taken an optimal size with  $W/L = 12\lambda/2\lambda$  and  $\lambda=0.023\mu m$ .

The function verifications and energy loss tests have been carried out for the 8-bit full adder with power-gating switches in different processes, frequencies and active ratios. At 90nm process, the total power consumption and leakage power consumption of the 8bit full adder with power-gating switches are shown in Table I and Table II, respectively. At 45nm process, the total power consumption and leakage power consumption of the 8bit full adder with power-gating switches are shown in Table III and Table IV.

Fig. 13 Logic gates based on P-DTGAL circuits used in the 8-bit full adder

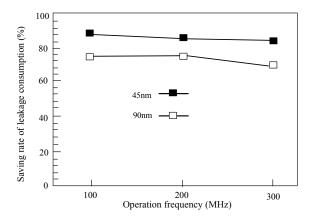

For comparison, an 8-bit full adder based on static CMOS logic circuits is also simulated. Fig. 14 shows saving rate of leakage consumption of the 8-bit full adder with the P-DTGAL power-gating switches to static CMOS implementation, which are 73.1% to 79.5% and 82% to 89.6% for clock rates ranging from 100 to 300MHz at a = 0.005 in 90nm process and 45nm process, respectively. The 8-bit adiabatic full adder using P-DTGAL power-gating schemes obtain more leakage loss savings in 45m CMOS process than 90nm CMOS process.

TABLE I

TOTAL POWER CONSUMPTION OF THE ADIABATIC 8-BIT CLA AT 90NM CMOS

| FROCESS (μW)                 |              |       |       |        |

|------------------------------|--------------|-------|-------|--------|

| Operation<br>Frequency (MHz) | ACTIVE RATIO |       |       |        |

|                              | 0.005        | 0.01  | 0.02  | 0.03   |

| 100                          | 2.349        | 2.698 | 3.396 | 4.014  |

| 200                          | 6.611        | 7.422 | 8.799 | 10.434 |

| 300                          | 7.57         | 9.14  | 12.28 | 15.18  |

TABLE II LEAKAGE POWER CONSUMPTION OF THE ADIABATIC 8-BIT CLA AT 90NM CMOS PROCESS ( $\mu W$ )

| Operation       | ACTIVE RATIO |       |       |       |

|-----------------|--------------|-------|-------|-------|

| Frequency (MHz) | 0.005        | 0.01  | 0.02  | 0.03  |

| 100             | 1.99         | 1.98  | 1.96  | 1.86  |

| 200             | 5.771        | 5.742 | 5.439 | 5.394 |

| 300             | 5.97         | 5.94  | 5.88  | 5.58  |

TABLE III TOTAL POWER CONSUMPTION OF THE ADIABATIC 8-BIT CLA AT 45NM CMOS

| Operation       | ACTIVE RATIO |       |       |        |

|-----------------|--------------|-------|-------|--------|

| Frequency (MHz) | 0.005        | 0.01  | 0.02  | 0.03   |

| 100             | 1.494        | 1.788 | 2.376 | 2.916  |

| 200             | 2.74         | 3.48  | 3.76  | 6.36   |

| 300             | 3.041        | 5.282 | 7.764 | 10.134 |

TABLE IV LEAKAGE POWER CONSUMPTION OF THE ADIABATIC 8-BIT CLA AT 45NM CMOS PROCESS ( $\mu$ W)

| Operation       | ACTIVE RATIO |       |       |       |

|-----------------|--------------|-------|-------|-------|

| Frequency (MHz) | 0.005        | 0.01  | 0.02  | 0.03  |

| 100             | 1.194        | 1.188 | 1.176 | 1.116 |

| 200             | 1.99         | 1.98  | 1.96  | 1.86  |

| 300             | 2.786        | 2.772 | 2.744 | 2.604 |

Fig. 14 Saving rate of leakage loss of the P-DTGAL 8-bit full adder with power-gating to static CMOS implementation in 90nm process and 45nm processes. Active ratio (a) = 0.005.

As can be seen from Fig. 14, with the scaling of device dimensions, more leakage loss can be saved by using the P-type adiabatic power-gating techniques, because both sub-threshold leakage and gate leakage of the P-type adiabatic circuits are all reduced compared with static ones.

### VII. CONCLUSION

In this paper, the adiabatic circuits with P-DTGAL power-gating techniques are investigated in terms of leakage power loss. The results show that the leakage loss of the adiabatic circuits can be reduced effectively by using P-DTGAL power-gating techniques.

### ACKNOWLEDGMENT

Project is supported by National Natural Science Foundation of China (No. 60773071) and the Zhejiang Science and Technology Project of China (No. 2007C11067 and 2009C31003), and supported by Ningbo Natural Science Foundation (No. 2009A610066).

#### REFERENCES

- N. S. Kim, T. Austin, J. S. Hu, and M. Jane, "Leakage current: Moore's law meets static power," Computer, vol. 38, no. 12, 2003, pp. 68-75.

- [2] F. Fallah and M. Pedram, "Standby and active leakage current control and minimization in CMOS VLSI circuits," *IEICE Transactions on Electronics*, vol. E88–C, no. 4, 2005, pp. 509–519.

- [3] A. Abdullah, F. Fallah, and M. Pedram, "Leakage current reduction in CMOS VLSI circuits by input vector control," *IEEE Trans Very Large Scale Integration (VLSI)*, vol. 12, no. 2, 2004, pp. 40-154.

- [4] A. B. Kahng, "Design challenges at 65nm and beyond," Proceedings of the Conference on Design, Automation and Test in Europe, Nice, France, 2007, pp. 1466-1467.

- [5] K. K. Kim, Y. B. Kim, M. Choi, and N. Park, "Leakage minimization technique for nanoscale CMOS VLSI," *IEEE Design and Test of Computers*, vol. 24, no. 4, Aug. 2007, pp. 322-330.

- [6] Y. Moon and D. K. Jeong, "An efficient charge recovery logic circuit", IEEE J. of Solid-State Circuits, vol.31, no. 4, 1996, pp.514–522.

- [7] Hu, Jianping, Li, Hong, Dong, Huiying, "A low-power adiabatic register file with two types of energy-efficient line drivers", *IEEE International Midwest Symposium on Circuits and Systems*, 2005, pp. 1753-1756.

- [8] P. Teichmann, J. Fischer, and S. Henzler, et al, "Power-clock gating in adiabatic logic circuits," in Proc. PATMOS'05, 2005, pp. 638–646.

- [9] Dong Zhou, Jianping Hu, and Huiying Dong, "An energy-efficient power-gating adiabatic circuits using transmission gate switches," *IEEE International Conference on ASIC* (AICON 2007), Guilin, China, 2007, pp. 145-148.

- [10] F. Hamzaoglu and M. R. Stan, "Circuit-level techniques to control gate leakage for sub-100nm CMOS," *Int. Symp on Low Power Electronics* and Design, 2002, pp. 60 – 63.

- [11] Wei Zhao and Yu Cao, "New generation of predictive technology model for Sub-45nm design exploration," Department of Electrical Engineering, Arizona State University, 2006.

- [12] A. Kramer, J. S. Denker, B. Flower, J. Moroney, "2nd order adiabatic computation with 2N-2P and 2N-2N2P logic circuits," *International* Symposium on Low Power Design, Dana Point, April 1995, pp. 191–196.

- [13] F. Liu, and K. T. Lau, "Pass-transistor adiabatic logic with NMOS pull-down configuration," *Electronics Letters*, vol. 34, no. 8, 1998, pp. 739-741.

- [14] Jianping Hu, Tiefeng Xu, Junjun Yu, and Yinshui Xia, "Low power dual transmission gate adiabatic logic circuits and design of SRAM," *IEEE International Midwest Symposium on Circuits and Systems*, Hiroshima, Japan, July 2004, pp.565-568.

- [15] D. Maksimovic and V. G. Oklobdzija, "Integrated power clock generators for low energy logic," *IEEE Power Electronics Specialists Conf., Atlanta*, GA, 1995, pp.61-67.