# Transformerless AC-DC Converter

Saisundar. S., I Made Darmayuda, Zhou Jun, Krishna Mainali, Simon Ng Sheung Yan, Eran Ofek

**Abstract**—This paper compares the recent transformerless AC-DC power converter architectures and provides an assessment of each. A prototype of one of the transformerless AC-DC converter architecture is also presented depicting the feasibility of a small form factor, power supply design. In this paper component selection guidelines to achieve high efficiency AC-DC power conversion are also discussed.

**Keywords**—AC-DC converter, digitally controlled, switched mode power supply, transformerless.

### I. INTRODUCTION

EFFICIENT AC-DC power conversion has been of much interest in recent years with the wide increase in electronic devices which demand clean DC power supplies. Today's industries aim to provide AC-DC adapters with very small form factors for portable applications like notebook charger, phone charger etc. The improvement in device technology has led to efficient and high power density devices. This has created tremendous improvement in AC-DC converters' size and efficiency.

The two typical methods of ac to dc conversion are the linear converters and switched mode converters. The linear converters use the standard topology of stepping down the voltage using a low frequency transformer and regulating the output voltage with a linear regulator. This architecture though simple suffers from low efficiency. The size of the transformer at line frequency of 50/60Hz is huge making it unsuitable for portable applications.

Switched mode power supplies have found a huge market because of their small form factor and high efficiency which make them suitable for portable applications. In order to meet the international regulations and standards [1]-[2] they require a two stage architecture. Power factor correction (PFC) stage followed by a DC-DC stage. A two stage approach mostly uses a boost PFC circuit for the first stage. This is because of the good PFC capability and high efficiency provided by this circuit. The consequence of using it in the first stage is the high voltage output which requires a capacitor with high voltage rating resulting in increase in size and cost. This voltage can reach very high values at low load conditions as indicated in [3]-[4].

Saisundar .S, I Made Darmayuda, Zhou Jun, Krishna Mainali and Simon Ng Sheung Yan are with Institute of Microelectronics, A\*STAR (Agency for Science, Technology and Research), 11 Science Park Road, Singapore Science Park II, Singapore 117685 (phone: 65-6770-5573; fax: 65-6774-5754; e-mail: sankas@ime.a-star.edu.sg).

Eran Ofek is working as Chief Scientist with Ney-Li Pte Ltd, 20 Cecil street, #14-01, Equity Plaza, Singapore 049705 (e-mail: eofek@ney-li.com).

Also, this approach is bit more complex due to two control loops, one for PFC and another for DC-DC converter.

Recently many single stage converter architectures have been reported [5]-[6]. The single stage architectures combine the PFC and DC-DC stage into a single stage reducing the control complexity. The PFC correction can also be done without the bridge rectifier and this architecture was first reported in [7] and is called bridgeless PFC.

This circuit combines the operation of the bridge rectifier with the DC-DC converter into a single circuit. The aim is to reduce the number of components and the size of components to obtain an energy efficient power supply design. This paper briefly reviews some of these architectures that can satisfy the requirements of the standards and provides a comprehensive review of the pros and cons of each. It also provides a feasibility study of one of the transformerless architecture to achieve a small size power converter for portable applications. Section II reviews the recent architectures in AC-DC conversion and provides a comparison, pointing to the important issues in power supply design that these architectures are aiming to solve.

Section III provides an implementation and feasibility of one of the transformerless AC-DC converter architecture with a digital controller. The measurement and simulation results are presented in section IV. Section V concludes with a summary.

## II. ARCHITECTURE REVIEW

A single stage approach combines the PFC stage and DC-DC converters to provide a less complex and compact solution. In applications where isolation is not a main concern one can choose architectures that can meet the specification and has a small size. One such architecture was presented in [5].

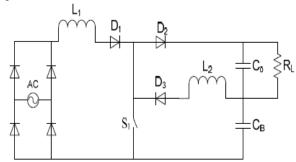

Fig. 1 Integrated Boost Buck-Boost SS AC-DC converter [5]

This converter is an Integrated Boost Buck-Boost single stage ac-dc converter as shown in Fig. 1. It uses the technique of direct power transfer to improve the efficiency and also keeps the voltage of the first stage at less than 400V in light load conditions.

This transformerless architecture does not need snubber circuits to damp oscillations associated with switching.

Thus, fewer components are required with reduced control complexity and physical dimensions of the converter. A 100W adapter meets the IEC61000-3-2 standard and also achieves a power factor of 0.976.

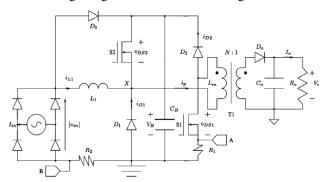

Another single stage converter proposed in [6] uses the boost PFC operating in DCM mode to obtain PFC correction. The output DC voltage is regulated with a fly back converter controlled by a single switch. The converter consists of a two transistor clamped fly back converter integrated with a boost PFC as a single stage converter as shown in Fig. 2.

Fig. 2 SS PFC with boost and clamped flyback converters [6]

This architecture aims at reducing the dc bus voltage regulation by adopting a clamped flyback converter operating with a dual current mode controller. It provides good power factor with lower current stresses on switches. It also provides isolation by using a flyback transformer. The paper reports a 100W adapter constructed with this architecture and the results satisfy the harmonic requirements set by IEC61000-3-2 and obtains an efficiency >75% at high loads.

The two architectures discussed so far use a boost PFC and require a good quality boost inductor and also an additional inductor or transformer along with a bridge rectifier which increases the size. These converters require good rectifiers with high heat dissipation capability, high current capability and low loss. The conduction loss of rectifiers and the forward voltage drop of the diodes limit the achievable efficiency. Hence to tackle these issues and to reduce the number of switching devices in the current path and thereby increase the efficiency many bridgeless PFC architectures have been proposed [7]-[9]. Two such architectures which use a SEPIC converter were reported in [10], [11].

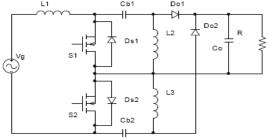

The schematic of the bridgeless SEPIC converter is shown in Fig. 3[11]. The advantage of using a SEPIC converter is that it provides an easy way to step up or step down the voltage. Hence the first stage does not need a high voltage capacitor. Also by adopting a bridgeless scheme the number of components that switch in a cycle is reduced greatly improving the efficiency. The SEPIC converter is operated in DCM mode to obtain good PFC. Also the controlling of MOSFET does not need an isolated drive making it simpler with a lesser number of components.

A 100W converter has been reported with an efficiency of more than 89% with a good power factor of 0.9 at high loads.

Fig. 3 Bridgeless SEPIC AC-DC converter [11]

The primary disadvantage of the scheme is the requirement of input inductors that operate at low frequency resulting in large size. Also the output capacitor needs to be huge to suppress the ripple. The circuit also suffers from 100Hz ripple at the output. Since SEPIC is a higher order converter, the control loop must be designed with care to avoid instability.

The paper [10] has also proposed a bridgeless SEPIC topology with low conduction losses. This converter also operates in DCM mode to achieve high power factor. This architecture needs an additional inductor in comparison with [11] resulting in increase in form factor and cost. But the three inductors can be coupled to give better performance reducing the EMI filter requirements. A 65W circuit was reported to achieve an efficiency of more than 90%.

Fig. 4 Bridgeless DCM SEPIC AC-DC converter [10]

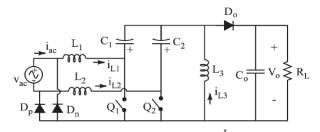

The architectures presented so far have aimed to obtain high efficiency as well as lower the first stage voltage. This results in reduction of the component sizes in the successive stages. The disadvantages of the architectures are mainly arising from the use of more number of inductors which is a hindrance in reducing the size. Another approach to achieve a lower first stage voltage is depicted in Fig. 5 [12].

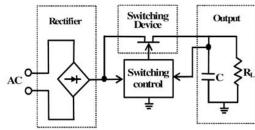

Fig. 5 AC-DC converter by chopping input [12]

The architecture consists of a rectifier, switching device and an output capacitor. The switch connects the input to the capacitor only when the input voltage is lower than the required voltage thereby limiting the voltage swing seen by the first stage capacitor which can have a lower voltage rating and size. The paper reported a 12V converter without using any inductors and high voltage capacitors though it suffers with the drawback of not providing electrical isolation.

| TABLE I                              |        |        |        |       |        |

|--------------------------------------|--------|--------|--------|-------|--------|

| COMPARISON OF EXISTING ARCHITECTURES |        |        |        |       |        |

| Parameters                           | [5]    | [6]    | [11]   | [10]  | [12]   |

| Power                                | 100W   | 100W   | 100W   | 65W   | 3W     |

| Efficiency %                         | >89    | >75    | >90    | >89   | NA     |

| # inductors                          | 2      | 1      | 2      | 3     | Nil    |

| #transformers                        | Nil    | 1      | Nil    | Nil   | Nil    |

| Input capacitor size                 | Nil    | Large  | Small  | Small | Medium |

| Output capacitor size                | Large  | Medium | Large  | Large | Nil    |

| Overall form-<br>factor              | Medium | Medium | Medium | Large | Small  |

#### III. PROPOSED ARCHITECTURE WITH DIGITAL CONTROLLER

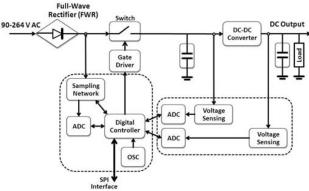

From the comparison Table I we see that the architecture [12] shows sufficient promise in reducing the size. By using a buck converter as the second stage very high efficiency and well regulated supply can be obtained. Hence this architecture with a digital controller was implemented on board with available off the shelf components and the controller for switching was implemented on FPGA. The architecture of the implemented converter is shown in Fig. 6.

Fig. 6 Proposed AC-DC converter with digital controller

It basically consists of 3 ADC's one to monitor the input, one to monitor the first stage output voltage and the third to monitor the DC-DC output. The digital controller implemented in FPGA uses this information to decide the switching instants and the output voltage level. The operation of the converter is as follows. The required output voltage is first set on the DC-DC converter controller and depending on this setting the first stage needs to provide a voltage level higher than this for the buck converter to operate properly.

Hence the first stage chops the input and sets the voltage of the capacitor to satisfy this requirement. The capacitor used in this first stage need not be huge as in [5] as the voltage regulation is taken care by the buck converter. The buck converter operates at 200kHz frequency and hence inductor required is small. By increasing the frequency to 1MHz the inductor size can be reduced greatly.

#### IV. MEASUREMENT AND SIMULATION RESULTS

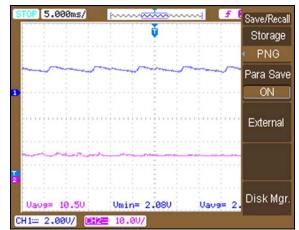

The output waveform of the converter prototype is as shown in Fig. 7. The DC-DC output in this case has been set to 10.5V and the first stage minimum voltage is set at more than 20V and we get a clean DC signal of 10.5V.

Fig. 7 Measurement waveform first stage output with 10x attenuation (upper) and dc-dc output (lower)

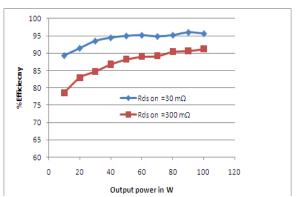

The architecture has a huge advantage that except the MOSFET switches, capacitor and the single buck inductor everything else can be integrated on chip. The buck converter can achieve close to 95% efficiency and hence it would be the switching stage that determines the overall efficiency. Simulation results of the switching stage using SPICE was performed for two different MOSFET models, one with an Rdson ("on resistance") of 30mOhms and another MOSFET with an Rdson of 300mOhms.

Fig. 8 Variation of first stage efficiency with MOSFET "on resistance"

The results in Fig. 8 show that with a MOSFET of 30mOhm "on resistance" the first stage is able to achieve an efficiency of more than 89% for most load conditions. Also the result clearly indicates the drop in efficiency with an increase in MOSFET "on resistance". The MOSFET chosen for the switching stage should have very low "on resistance" to minimize the switching losses. Also the rectifier should be chosen to minimize the losses. In applications where isolation is primary concern, a fly back dc-dc converter can be used in the second stage that provides transformer isolation instead of a simple buck converter. The transformer will need to deal with lower voltage when compared to the ones in [6] and can operate at 1MHz frequency and hence the size can be made very small with a slight drop in efficiency.

## V.CONCLUSION

This paper reviewed various recent transformerless architectures. A prototype of a non-isolated transformerless AC-DC converter was demonstrated that indicates the feasibility of designing an AC-DC converter with small form factor and good efficiency.

#### REFERENCES

- [1] "IEEE Std 519-992: IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems," *Institute of Electrical and Electronics Engineers*, 1992.

- [2] "IEC61000-3-2: 2005-11 Third Edition, EMC Part 3-2:"Limits for harmonic current emissions (Equipment input current ≤16 A per phase).

- [3] Q. Jinrong, Z. Qun, and F. C. Lee, "Single-stage single-switch powerfactor-correction AC/DC converters with DC-bus voltage feedback for universal line applications," *IEEE Transactions on Power Electronics*, vol. 13, no.6, pp. 1079-1088, Nov. 1998.

- [4] L. Shiguo, W. Huai, Z. Guangyong, and I. Batarseh, "Several schemes of alleviating bus voltage stress in single stage power factor correction converters," in *Power Electronics and Drive Systems*, vol.2, pp.921-926, Jul. 1999.

- [5] S.K.Kyi, and D.D.C.Lu "Transformerless single-stage AC/DC Converter with direct power transfer" in *Power Engineering Conference*, 2008. AUPEC '08. Australasian Universities, pp.1-6, Dec. 2008.

- [6] D. D. C. Lu, H. H. C. Iu, and V. Pjevalica, "A single-stage AC/DC converter with high power factor, Regulated bus voltage, and Output voltage," *IEEE Transactions on Power Electronics*, vol. 23, no.1, pp. 218-228, Jan. 2008.

- [7] D. M. Mitchell, "AC-DC converter having an improved power factor," U.S. Patent 4 412 277, Oct. 25, 1983.

- [8] U. Moriconi, "A bridgeless PFC configuration based on L4981 PFC controller," Appl. Note AN1606, ST-Microelectronics, Geneva, Switzerland, Nov. 2002.

- [9] G. Moschopoulos and P. Jain, "A novel single-phase soft-switched rectifier with unity power factor and minimal component count," *IEEE Transactions on Industrial Electronics*, vol. 51, no. 3, pp. 566–576, Jun. 2004.

- [10] SABZALI et al, "New Bridgeless DCM Sepic and Cuk PFC Rectifiers with Low Conduction and Switching Losses," in *IEEE transactions on industrial applications*, vol.42, no.2, pp.873-881, Apr. 2011.

- [11] M.R. Sahid.; A.H.M. Yatim, T. Taufik, "A New AC-DC Converter Using bridgeless SEPIC", in *IECON2010*, pp.286-290, Nov. 2010.

- [12] M.S. Lee; Y.C. Cho; H.W. Cha; "A novel AC-DC Converter unrequiring inductors for power conversion," in *Applied power electronics conference and exposition*, pp.1358,Feb. 2008.