# Effects of Capacitor Bank Defects on Harmonic Distortion and Park's Pattern Analysis in Induction Motors

G. Das, S. Das, P. Purkait, A. Dasgupta, and M. Kumar

Abstract—Properly sized capacitor banks are connected across induction motors for several reasons including power factor correction, reducing distortions, increasing capacity, etc. Total harmonic distortion (THD) and power factor (PF) are used in such cases to quantify the improvements obtained through connection of the external capacitor banks. On the other hand, one of the methods for assessing the motor internal condition is by the use of Park's pattern analysis. In spite of taking adequate precautionary measures, the capacitor banks may sometimes malfunction. Such a minor fault in the capacitor bank is often not apparently discernible. This may however, give rise to substantial degradation of power factor correction performance and may also damage the supply profile. The case is more severe with the fact that the Park's pattern gets distorted due to such external capacitor faults, and can give anomalous results about motor internal fault analyses. The aim of this paper is to present simulation and hardware laboratory test results to have an understanding of the anomalies in harmonic distortion and Park's pattern analyses in induction motors due to capacitor bank defects.

**Keywords**—Capacitor bank, harmonic distortion, induction motor, Park's pattern, PSCAD simulation.

### I. INTRODUCTION

An induction machine requires reactive power for operation. Thus its power factor is inherently poor, and it is worse especially at starting and when running with light loads or also when operating with power electronics converter [1].when operating at a lagging power factor, a power system requires additional VAr flow, which results in reduced system capacity, increased system losses, reduced system voltage and Also result in additional costs in the form of penalties [2].

Harmonic current generated by the motor load flows from the load into the power system [3]. The harmonic-laden power system current is then imposed on all of the remaining loads connected to the system. This current distortion may result in more harmonics generation.

The reactive power consumption is traditionally minimized (power improvement) by connecting shunt capacitors to the terminals of the motor. Shunt capacitors connected to the

G. Das (email: goutam\_y2k@yahoo.co.in), S. Das (e-mail: santanu\_das@ieee.org), P. Purkait (email: praj@ieee.org), A. Dasgupta (e-mail: arnab.ee.hit@gmail.com) and M. Kumar (e-mail: manishlohani.ee@gmail.com) are with the Department of Electrical Engineering, Haldia Institute of Technology, Haldia, Midnapore(E), West Bengal – 721 657, India.

terminals of the motor supply the reactive power to counteract some or the entire lagging component of the inductive load current of the induction motor [4].

The correcting capacitors, often connected in banks on smaller units, may fail in part due to one reason or the other. This creates a severe situation by deteriorating the PF correction scheme and often confusing the motor protection relay settings or any other motor monitoring devices used.

Aim of this research project is to investigate the effects of malfunction of capacitor bank connected in parallel with the motor on Concordia patterns, THD and power factor.

#### II. CAPACITOR BANK FAILURES

There are a number of ways in which a capacitor bank may be connected, with the choice being dependent on the voltage level of the system, the KVAr capacity of the bank, the system grounding, and the desired relay protection.

A capacitor bank of a given size and voltage rating may be made up of a number of series groups of capacitors, and a number of parallel capacitors per series group.

Each capacitor unit is typically protected by an individual fuse, externally mounted between the capacitor unit and the capacitor bank fuse bus. With internally fused capacitors, when a capacitor pack or element fails, the current, through its individual fusible link, will be considerably higher than the normal current. This higher current will blow the fusible link, thereby isolating the failed pack or element [5].

When a fuse blows in a capacitor bank, an increase in the fundamental frequency voltage occurs on the remaining units in that series group. An unbalance detection scheme is employed to monitor such conditions and to take action as required.

Unbalance protection normally provides the primary protection for arcing faults within a capacitor bank and other abnormalities that may damage capacitor units and or fuses. Arcing faults may cause substantial damage in a small fraction of a second [6]. The unbalance protection should have minimum intentional delay in order to minimize the amount of damage to the bank in the event of external arcing.

# III. CONCORDIA PATTERN ANALYSIS FOR MOTOR FAULT DIAGNOSIS

One of the potential methods of induction motor fault

detection based on the analysis of the line currents is the Concordia vector or Park's vector approach [7-10]. In Park's Vector representation, ellipticity of the figure increases with the severity of the fault and its major axis orientation is associated to the faulty phase. Detailed theoretical background for obtaining Park's pattern from 3 phase stator currents can be found in [7-10].

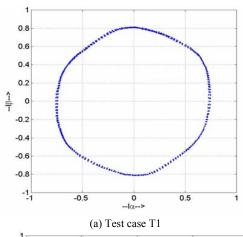

The current Concordia vector (plot between  $I\alpha$  and  $I\beta$ ) is a circular pattern centered on the origin of the coordinates. Under balanced supply voltage condition and a healthy motor with balanced load, the corresponding  $\alpha\beta$  stator current components trajectories create a uniform circle in the state space [8, 11]. This acts as a reference figure that allows the detection of abnormal conditions by monitoring the deviations of acquired patterns.

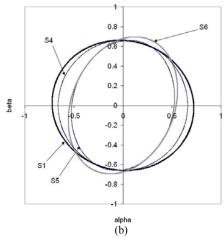

In the case of a fault in the stator winding, the  $\alpha\beta$  trajectory no longer remains circular, but becomes elliptic whose major axis orientation is associated to the faulty phase. Such a situation is reproduced from [11] and is shown in Fig. 1

Fig. 1 Current Concordia pattern for faulty condition [18]

## IV. LABORATORY TEST RESULTS

# A. Simulation using PSCAD

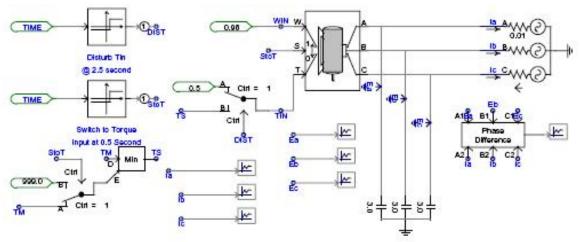

Power Systems Computer Aided Design (PSCAD) is a

simulation software with which complex networks and control systems can be simulated. Power quality disturbances such as capacitor switching and voltage sags events with emphasis on system faults and induction motor starting are of particular interest [12]. Computer simulation results indicate that the software can be utilized as an effective tool for simulating power quality problems [13].

In the present work, PSCAD has been used to construct model of a three phase induction motor, supplied from a balanced three phase supply through a capacitor bank. The simulation model in PSCAD is shown in Fig. 2. Faults have been simulated in the capacitor banks in three different phases and line currents are recorded. Average power factor and THD of the line current signal have been computed for different cases, as were Concordia patterns generated.

Simulation Test Observations and Results Analysis

From Table I, it is observed that PF values are higher for cases with higher degree of capacitor unbalancing. THD values are also found to be increasing with degree of unbalancing in capacitor bank. Any power quality monitoring device connected to such a system thus, may indicate anomalous results about harmonic distortion.

Study Capacitance/ Power Total

Point phase(µf) factor harmonic

distortion

TABLE I

| 1 OIIIt | phase(μ1) |   |   | ractor | distortion |

|---------|-----------|---|---|--------|------------|

|         | R         | Y | В | -      | (THD)      |

| S1      | 3         | 3 | 3 | 0.88   | 4.71       |

| S2      | 7.5       | 3 | 3 | 0.872  | 4.73       |

| S3      | 7.5       | 3 | 1 | 0.885  | 4.74       |

| S4      | 3         | 3 | 1 | 0.908  | 4.76       |

| S5      | 3         | 3 | 7 | 0.872  | 4.88       |

| S6      | 1         | 3 | 7 | 0.885  | 4.92       |

Fig. 3 gives plot of the recorded three-phase current wave and the derived  $\alpha$ - $\beta$  component currents corresponding to test cases S1 and S4. S1 represent a balanced capacitor bank test case, while S4 is for an unbalanced case. The variations and unbalancing in the current waves due to capacitor bank failure

Fig. 2 PSCAD simulation model

is clearly visible in Fig. 3(b). Similar plots can be obtained for the other test cases. Concordia patterns obtained by plotting  $\alpha$  vs.  $\beta$  component currents for test cases S1-S6 are plotted in Fig. 4  $\alpha$  and  $\beta$  axes are plotted in terms of per unit values where the instantaneous values are divided by peak of rated motor line current.

Fig. 3 Three phase current and  $\alpha$ - $\beta$  component currents for test case (a) S1 and (b) S4

Fig. 4 Concordia patterns corresponding to test cases (a) S1 - S3 and (b) S4 - S6

As can be seen in Fig. 4(a) and Fig. 4(b) that the Concordia pattern corresponding to the healthy condition S1 is a perfect circle. However for other cases (S2 – S6) with different degrees of unbalance in capacitance connected in the three phases, the Concordia pattern is found to deviate from its regular circular shape to more elliptical shape with different angles and different directions of inclination.

### B. Hardware Test Details

The test setup shown in Fig. 5 consists of one laboratory grade 1.5 kW, 3-phase, 440V, 50 Hz induction motor along with a capacitor bank with series parallel combination of six capacitors (1 $\mu$ F and 2.25 $\mu$ F, three each) in each phase. A number of variations could thus be obtained by different combinations of the externally connected capacitors in each phase. Motor line currents are measured with YOKOGAWA power meter [Model WT230], and then transferred to the PC for further analysis. Table II summarizes the different test conditions with corresponding values of THD and power factors.

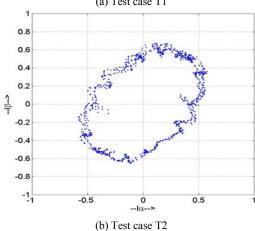

### C. Hardware Test Observations and Results

Observing Table II, PF values are found to be poorer and much more unpredictable in the case of unbalanced capacitor banks (T2-T5) as compared to the test case T1 where balanced capacitor bank is used. THD values are also found to be increasing with degree of unbalancing in capacitor bank. Any power quality monitoring device connected to such a system thus, may indicate anomalous results about harmonic distortion.

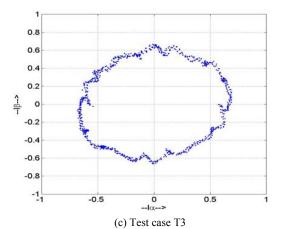

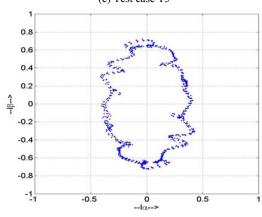

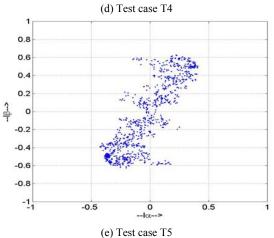

Concordia patterns obtained by plotting  $\alpha$  vs.  $\beta$  component currents for test cases T1-T5 are plotted in Fig. 6.  $\alpha$  and  $\beta$  axes are plotted in terms of per unit values where the instantaneous values are divided by peak of rated motor line current.

Fig. 5 Laboratory experimental setup

TABLE II

| STUDY POINTS WITH LABORATORY AND FIELD MOTOR |                        |   |     |                            |      |      |       |  |  |  |  |

|----------------------------------------------|------------------------|---|-----|----------------------------|------|------|-------|--|--|--|--|

| Study                                        | Capacitance/phase (μF) |   |     | Power Factor of each phase |      |      | THD   |  |  |  |  |

| Point                                        | R                      | Y | В   | R                          | Y    | В    | %     |  |  |  |  |

|                                              |                        |   |     |                            |      |      |       |  |  |  |  |

| T1                                           | 3                      | 3 | 3   | 0.72                       | 0.74 | 0.76 | 9.20  |  |  |  |  |

| T2                                           | 7.5                    | 3 | 7.5 | 0.49                       | 0.67 | 0.78 | 13.60 |  |  |  |  |

| T3                                           | 7.5                    | 3 | 3   | 0.63                       | 0.6  | 0.68 | 15.23 |  |  |  |  |

| T4                                           | 3                      | 3 | 0   | 0.46                       | 0.79 | 0.67 | 15.90 |  |  |  |  |

| T5                                           | 7.5                    | 3 | 0   | 0.14*                      | 0.8  | 0.77 | 19.90 |  |  |  |  |

<sup>\*</sup> Leading power factor

Fig. 6 Concordia patterns for test cases T1-T5 (a-e respectively)

It is clearly evident from the Concordia patterns shown in Fig. 6 that unbalance in capacitor bank drastically changes the shape of the pattern. The amount of distortion of Concordia pattern is largely related to unbalance in the capacitor bank values. Any assessment of the motor internal condition based on these Concordia patterns will thus be anomalous. The extremely distorted Concordia pattern shown in Fig. 6 (e) is attributed to the harmonic prone and completely unbalanced three phase current pattern of T5.

#### V. CONCLUSION

Properly designed capacitor banks when connected to induction motors can improve the power factor among other improvements in overall performance. Any malfunction of the capacitor bank (even partially) can, however, cause unwanted degradation of system performance. Power supply distortions normally can be quantified by PF and THD, whereas Concordia pattern analysis can be used to assess motor internal condition. Simulation and laboratory hardware test results presented in this paper illustrates how malfunction of capacitor bank can give anomalous indication of both supply irregularities (in terms of PF and THD) and motor condition (in terms of Concordia patterns). Enough precautions are thus essential to comment on harmonic distortion and Concordia pattern analyses in induction motors in the presence of capacitor banks.

#### REFERENCES

- [1] A. A. Jimoh, and D. V. Nicolae, "A study of improving the power factor of a three-phase induction motor using a static switched capacitor", in Proc. 12th International Power Electronics and Motion Control Conference, EPE-PEMC, pp. 1088 – 1093, 2006.

- [2] R. A. Fuselier, "Alternative cost-effective applications of power factor correction," *IEEE Trans. Industry Applications*, vol. 25, no. 1, pp. 10 – 18, January 1989.

- [3] R. Yacamini, "Power system harmonics: Part 3. Problems caused by distorted supplies", *Power Engineering Journal*, vol. 9, no. 5, pp. 233 – 238, Oct. 1995.

- [4] R. Spee, A. K. Wallace, "Comparative evaluation of power factor improvement techniques for squirrel cage induction motors", *IEEE Trans. Industry Applications*, vol. 28, no. 2, pp. 381 – 386, March-April 1992.

- [5] IEEE Guide for the Protection of Shunt Capacitor Banks, IEEE Standard C37.99-2000.

- [6] IEEE Guide for Application of Shunt Power Capacitors, IEEE Standard 1036-1992.

- [7] A.J. Marques Cardoso, S.M.A. Cruz and D.S.B. Fonseca, "Inter-turn stator winding fault diagnosis in three-phase induction motors, by Park's vector approach", *IEEE Trans. Energy Conversion*, vol. 14, no. 3, pp. 595 – 598, Sept. 1999.

- [8] F. Zidani, M.E.H. Benbouzid, D. Diallo and M.S. Nait-Said, "Induction motor stator faults diagnosis by a current Concordia pattern-based fuzzy decision system", *IEEE Trans. Energy Conversion*, vol. 18, no. 4, pp. 469 – 475 Dec. 2003

- [9] H. Nejjari and M.E.H. Benbouzid, "Monitoring and diagnosis of induction motors electrical faults using a current Park's vector pattern learning approach", *IEEE Trans. Industry Applications*, vol. 36, no. 3, pp. 730 – 735, May 2000.

- [10] S. Das, P. Purkait, and S. Chakravorti, "Space-Vector characterization of induction motor operating conditions", in *Proc.* 15<sup>th</sup> NPSC, IIT Mumbai, pp. 512 – 517, Dec 2008.

- [11] J.F. Martins, V.F. Pires and A. J. Pires, "Unsupervised neural-network-based algorithm for an on-line diagnosis of three-phase induction motor stator fault", *IEEE Trans. Industrial Electronics*, vol. 54, no. 1, Feb. 2007, pp. 259–264.

- [12] J.V. Milanovic, M.T. Aung, and S.C.Vegunta., "The Influence of Induction Motors on Voltage Sag Propagation—Part I: Accounting for the Change in Sag Characteristics", *IEEE Trans. Power Delivery*, vol. 23, no. 2, pp. 1063 – 1071, April 2008.

- [13] M.A. Hannan and A. Mohamed, "PSCAD/EMTDC simulation of unified series-shunt compensator for power quality improvement", *IEEE Trans. Power Delivery*, vol. 20, no. 2, pp. 1650 – 1656, April 2005.

Goutam Das was born in Purba Medinipur, India in 1983. He obtained his B.Tech and M.Tech degrees from Haldia Institute of Technology, Haldia, India in 2006 and 2008 respectively. Presently he holds the post of Lecturer, Department of Electrical Engineering Haldia Institute of Technology, Haldia, India. His current research includes condition assessment techniques.

Santanu Das (M'05) was born in Hooghly, India, in 1977. He obtained his B.E.E and M.E.E. from Bengal Engineering and Science University, Howrah, India in the year 1998 and 2001 respectively. He worked at HCL Perot Systems Ltd., India and also at Asansol Engineering College. He is currently employed as a Assistant Professor in Electrical Engineering Department, Haldia Institute of Technology. His current research interests include PD simulation and analysis, PLC based motion control, Power Electronics and Drives, Motor condition monitoring.

Prithwiraj Purkait (M '97, SM '10) was born in Kolkata, India in 1973. He obtained his B.E.E., M.E.E. and PhD degrees from Jadavpur University, Kolkata, India in 1996, 1999 and 2002 respectively. He worked with M/s Crompton Greaves Ltd, Mumbai, India as a Design Engineer for one year. He was involved in post-doctoral research in the University of Queensland, Australia during 2002-2003, and further as Visitng Academic during 2005 and 2007. Presently he holds the post of Professor and Head, Department of Electrical Engineering Haldia Institute of Technology, Haldia, India. His current research includes transformer insulation condition assessment techniques and advanced signal processing applications in High Voltage Engineering.

**Arnab Dasgupta** (M'07) was born in Dhanbad, Jharkhand, India in 1988. Presently he is a final year B. Tech student of Department of Electrical Engineering Haldia Institute of Technology, Haldia, India.

Manish Kumar (M'07) was born in Patna, India in 1986. Presently he is a final year B. Tech student of Department of Electrical Engineering Haldia Institute of Technology, Haldia, India.