# Improvement of Short Channel Effects in Cylindrical Strained Silicon Nanowire Transistor

Fatemeh Karimi \*, Morteza Fathipour\*, Hamdam Ghanatian\* and Vala Fathipour\*

Abstract-In this paper we investigate the electrical characteristics of a new structure of gate all around strained silicon nanowire field effect transistors (FETs) with dual dielectrics by changing the radius (R<sub>SiGe</sub>) of silicon-germanium (SiGe) wire and gate dielectric. Indeed the effect of high-k dielectric on Field Induced Barrier Lowering (FIBL) has been studied. Due to the higher electron mobility in tensile strained silicon, the n-type FETs with strained silicon channel have better drain current compare with the pure Si one. In this structure gate dielectric divided in two parts, we have used high-k dielectric near the source and low-k dielectric near the drain to reduce the short channel effects. By this structure short channel effects such as FIBL will be reduced indeed by increasing the  $R_{SiGe}$ ,  $I_D$ - $V_D$  characteristics will be improved. The leakage current and transfer characteristics, the threshold-voltage (Vt), the drain induced barrier height lowering (DIBL), are estimated with respect to, gate bias (V<sub>G</sub>), R<sub>SiGe</sub> and different gate dielectrics. For short channel effects, such as DIBL, gate all around strained silicon nanowire FET have similar characteristics with the pure Si one while dual dielectrics can improve short channel effects in this structure.

*Keywords*—SNWT (silicon nanowire transistor), Tensile Strain, high- $\kappa$  dielectric, Field Induced Barrier Lowering (FIBL), cylindrical nano wire (CW), drain induced barrier lowering (DIBL).

## I. INTRODUCTION

DRIVING capability of strained silicon (Si) field effect transistors (FETs) make them more attractive than pure Si-based FETs. Compared with the pure Si-based FET, the strained FET has a slightly higher leakage current due to the silicon germanium (SiGe) channel film has a lower bandgap[1]-[6]. Multiple gate structures are considered as

\*Fatemeh Karimi is with Islamic Azad University Central branch, Tehran, Iran. Young Researchers Club, student member of IEEE(phone: +989122824167; email: fm\_karimi779@yahoo.com

<sup>2</sup>M. Fathipour is the head of the Device and Simulation Lab., he is an IEEE member and is the associate professor of the Department of Electrical and Computer Engineering of the University of Tehran, P.O. Box 14395-515,Tehran, Iran (corresponding author to provide mobile: (+98 912) 147 32 09; phone: (+98 21) 88 02 04 03; e-mail: mfathi@ut.ac.ir).

<sup>3</sup>Islamic Azad University Central branch, Tehran, Iran., ghanatian\_hamdam@yahoo.com

<sup>4</sup>Vala Fathipour is the postgraduate student of the Department of Electrical and Computer Engineering of the University of Tehran, P.O. Box 14395-515, Tehran, Iran (email:valafathi@gmail.com).

<sup>\*</sup>This research was carried out at the Device Modeling and Simulation Laboratory of the Department of Electrical and Computer Engineering of the University of Tehran.

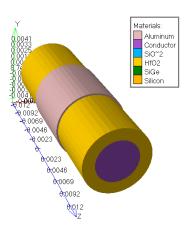

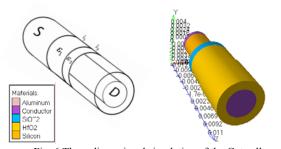

Fig.1 Simulated strained nano wire field effect transistor

promising candidates to overcome short channel effects (SCE) usually encountered in nano-scale MOSFET.

They have better transport characteristics and improved short channel effects (SCEs) than that of single gate (SG) FETs [7] - [11]. Pure Si-based gate all around transistors have the best channel controllability and lowest SCEs among different structures of FETs [12]-[14]. In this paper, a new structure of gate all around stained Si nanowire FET with various gate dielectrics will be investigated as shown in fig.1. High- $\kappa$  dielectrics are using to compensate the thick oxide. By using the High-k dielectrics gate control increases and drain current will be improved while fringing drain field can affect to barrier height easily and result in increasing the short channel effects [5]-[18]. To reduction this effects we used low-k dielectric near the drain to control the DIBL effects. We find that the gate all around strained Si nanowire FETs exhibit higher on-state current and sustain almost the same off-state current and short channel effects, compared with the surrounding-gate Si nanowire FETs. Combinative dielectrics of high-k and low-k could help to improve the short channel effects and get the high speed structures. However, the surrounding-gate strained Si nanowire FET sustains the similar I<sub>on</sub>/I<sub>off</sub> current ratio, the threshold voltage roll-off, and SCEs, compare with the characteristics of pure Si one. The paper is organized as follows. In section 2, we describe the device and its structural parameters. Section 3 describes the simulation results. Section 4 draws conclusions.

# II. DEVICE STRUCTURE

We have simulated a cylindrical gate all around strained SNWT with dual dielectrics as shown in fig.1. The structure is with a SiGe nanowire covered by a layer of Si. The composition of  $Si_xGe_{1-x}$  of the *n*-type FET is fixed at x = 0.8in our simulation. In these analyses the gate length is 8nm, gate is made of aluminum and its work function is 4.1 eV. The oxide thickness is 2nm, the channel is P-doped with  $N_A = 10^{17} (cm^{-3})$  and the source and drain are doped with  $N_d =$  $10^{20}(cm^{-3})$ . The radius of Si and SiGe is equal to 2.5 nm, and transport is along z direction. Full quantum mechanical models are the most accurate ways to study such nano scale devices. 3D density-gradient drift-diffusion model is used in this simulation [12]-[14]. In this study we work on device characteristic optimization with respect to various physical parameters including R<sub>SiGe</sub>, composition effects of Si<sub>x</sub>Ge<sub>1-x</sub> and Lhigh-k/Llow-k.

# III. RESULTS AND DISCUSSIONS

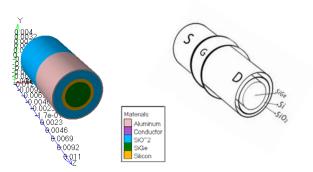

Fig. 2 Three dimensional simulation of the Gate all around Cylindrical strained SNWT with different SiGe radius

# A. Strained Silicon Channel

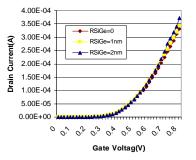

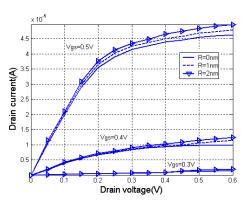

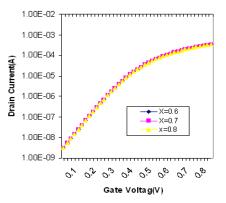

Figure 3 shows the  $I_D - V_G$  curves of the gate all around strained Si FETs with different  $R_{SiGe}$ . Results confirm that by increasing the  $R_{SiGe}$  transfer characteristic doesn't change alot thus threshold voltage and  $I_{ON}/I_{OFF}$  ratio are the same for pure Si and strained Si nano wire transistors. Band gap of SiGe is intrinsically smaller than that of pure Si, but the leakage current does not influenced. This consequence is caused from the fact that gate all around nanowire FETs have excellent gate control. Therefore, leakage current can not improve the on state current. Fig. 4, Shows the  $I_D - V_D$  curves of the gate all around strained Si nanowire FET. Strained SNWT with  $R_{SiGe} = 1$  and 2 nm, respectively, has a higher drain current than that of the pure Si one (solid lines). The larger radius ( $R_{SiGe} = 2$  nm) of SiGe implies the higher drain current due to a higher stress caused from the thicker SiGe radius. The lower source/drain parasitic resistance caused from the SiGe layer plays another factor for the enhancement of the on-state current [19].

Fig. 3  $I_{DS}$  verses gate voltage in SNWT with different  $R_{SiGe}$  $V_{DS}=0.5V$

Fig. 4 The computed  $I_D - V_D$  curves of the FET with different  $R_{SiGe}$ .

Fig. 5 The computed  $I_D$  –V\_G curves of the FET with different X.composition  $(Si_xGe_{1-x}),V_{DS}{=}0.5V$

In fig. 5 transfer characteristic are plotted for different X.composition. the results show that drain current has not been influenced by changing the composition.

Fig. 6 Three dimensional simulation of the Gate all around Cylindrical strained SNWT with dual gate dielectrics and  $R_{siGe}$ =1.5nm

### B. Dual dielectrics

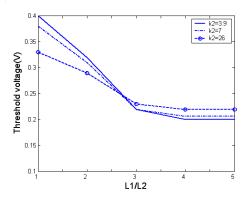

In this section we are going to improve the short channel effects by using the Combinative dielectrics of high- $\kappa$  in all structure and low- $\kappa$  dielectric near the drain as shown in fig.6. High- $\kappa$  materials are using to improve the gate control in stead of thin oxide layer. On the other hand these materials cause to increasing the drain fringing field effects on the channel and FIBL increases. Therefore the use of a low- $\kappa$  material near the drain could help to reduce the FIBL. In fig. 7 the effect of two dielectrics length rate on threshold voltage is investigated for different dielectric constant at drain side. In this study the dielectric constant of gate is 26 and the dielectric constant at drain side is changes from 26 to 3.9. As the figure shows by considering the rate  $L_{high-\kappa}/L_{low-\kappa}$  equal to 3 or upper, threshold voltage will be almost constant.

Fig. 7 The effect of dielectrics length rate on threshold voltage with dual gate dielectrics and  $R_{SiGe}$ =1.5nm (L<sub>1</sub> is high- $\kappa$  dielect and L<sub>2</sub> is low- $\kappa$  length)

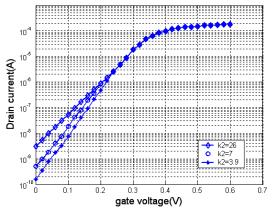

In fig.8 the effect of dual gate dielectrics on transfer characteristics is plotted. In this simulation  $R_{SiGe}$  is 1.5 nm and  $L_1/L_2$  ratio is equal to 3.  $\kappa_1$  is dielectric constant at source side and  $\kappa_2$  is dielectric constant at drain side.

The result shows that by decreasing the dielectric constant at drain side off state current reduces as well as reduction in short channel effects.

Fig. 8 The effect of dielectrics constant at drain side on I<sub>D</sub>-V<sub>GS</sub> characteristic in strained silicon nano wire transistor with R<sub>siGe</sub>=1.5nm (k<sub>1</sub> is high-κ dielectric and k<sub>2</sub> is low-κ dielectric)

By this structure we could reduce the short channel effects and off state current as shown in table 1.

TABLE I THE EFFECT OF DIELECTRIC CONSTANT AT DRAIN SIDE ON FIBL AND OFF STATE CURRENT

| TIBETING OTT STATE CONDENT           |      |                      |

|--------------------------------------|------|----------------------|

| $l_1/l_2 = 3$ , $\varepsilon_1 = 26$ | FIBL | $I_{OFF}$            |

| $\varepsilon_2 = 26$                 | 517  | 3.21e <sup>-9</sup>  |

| $\varepsilon_2 = 7$                  | 342  | 6.09e <sup>-10</sup> |

| $\varepsilon_2 = 3.9$                | 168  | $1.52e^{-10}$        |

# IV. CONCLUSION

We have investigated a new structure of cylindrical strained SNWT with dual gate dielectrics. We have studied the effect of  $R_{SiGe}$  on the electrical characteristics of the gate all around strained Si nanowire FET using a 3D device simulation by ATLAS simulator [20].  $R_{SiGe}$  can change the driving current of our structure. When  $R_{SiGe}$  is increased, the driving current is increased. However, it does not have significant effects on the transfer characteristics. In this structure strain can not improve the short channel effects, the  $I_{on}/I_{off}$  ratio or any changes in threshold voltage. Because of excellent gate control in gate all around structures, gate leakage current negligibly increase the on state current. To reduce the short channel effects and improve the  $I_{on}/I_{off}$  ratio dual gate dielectrics is used. Length ratio  $(L_1/L_2)$  is chosen equal to 3, to keep the threshold voltage off changing by dielectric constant. Simulation results have shown that this structure of gate all around strained Si nanowire FET is attractive to application of high speed nano devices. Low source/drain parasitic resistance, high driving current, low off state current, high gate control and low short channel effects are the significant characteristics of this structure. By this structure the Field Induced Barrier Lowering reduced about 350mV/V which indicates to high gate control in this gate all around silicon nano wire structure.

#### REFERENCES

- H.M. Nayfeh et al., "Influence of high channel doping on the inversion layer electron mobility in strained silicon n-MOSFETs," *IEEE Elec. Dev. Lett.*, 24, 248 (2003).

- [2] B.H. Lee et al., "Performance enhancement on sub-70 nm strained silicon SOI MOSFETs on ultra-thin thermally mixed strained silicon/SiGe on insulator (TM-SGOI) substrate with raised S/D," *Tech. Dig. IEDM* 946 (2002).

- [3] C. Fenouillet-Beranger et al., "Requirements for ultra-thin-film devices and new materials for the CMOS roadmap," *Solid-State Elec.*, 48, 961 (2004).

- [4] K. Rim et al., "Fabrication and analysis of deep submicron strained-Si n-MOSFET's," *IEEE Trans. Elec. Dev.*, 47, 1406 (2000).

- [5] L. Huang et al., "Electron and hole mobility enhancement in strained SOI by wafer bonding," *IEEE Trans. Elec. Dev.*, 49, 1566 (2002).

- [6] J.R. Hwang et al., "Performance of 70 nm strained-silicon CMOS devices," *Dig. Tech. 2003 Symp. VLSI Tech.*, 103 (2003).

- [7] J.Wang, E. Polizzi, M. Lundstrom, A three-dimensional quantum simulation of silicon nanowire transistors with the effective-mass approximation, J. Appl. Phys. 96 (2004) 2192–2203.

- [8] R. Venugopal et al., "Simulating quantum transport in nanoscale transistors: Real versus mode-space approaches," J. App. Phys., 92, 3730 (2002).

- [9] J.Wang et al., "Does source-to-drain tunneling limit the ultimate scaling of MOSFETs?," *Tech. Dig. IEDM*, 707 (2002).

- [10] A. Svizhenko et al., "Role of scattering in nanotransistors," *IEEE Trans. Elec. Dev.*, 50, 1459 (2003).

- [11] H. Kawaura et al., "Observation of source-to-drain direct tunneling current in 8 nmgate electrically variable shallow junction metal-oxidesemiconductor field-effect transistors," *Appl. Phys. Lett.*, 76, 3810 (2000).

- [12] M. Rashed et al., "Simulation of electron transport in strained silicon on relaxed Sil-xGex substrates," in *Proc. Biennial University/ Government/Industry Microelec. Symp.* (1995) vol. 168.

- [13] A. Schenk et al., "2D Analysis of source-to-drain tunneling in decananometer MOSFETs with the density-gradient model," in Proc. 5th Int. Conf. Modeling and Simulation of Microsystems, ed. M. laudon and B. Romanowicz,pp.552-555, San Juan, 2002.

- [14] S.N. Balaban et al., "Quantum transport in a cylindrical sub- 0.1  $\mu$ m silicon-based MOSFET," *Solid-State Elec.*, 46, 435 (2002).

- [15] X. Loussier, D. Munteanu, J.L. Autran Journal of Non-Crystalline Solids 355 (2009) 1185–1188.

- [16] M. Houssa (Ed.), Fundamental and Technological Aspects of High-j Gate Dielectrics, IOP, London, 2004.

- [17] M. Houssa et al., MRS Symp. Proc. 177 (2004).

- [18] B. Cheng et al., IEEE Trans. Electr. Dev. 46 (2003) 1537.

- [19] YIMING LI, JAM-WEM LEE, Journal of Computational Electronics 3: 251–255, 2004.

- [20] Silvaco International, Atlas User's Manual, 2008.